Protocol Dictates Requirements For RFID ICs

Growth in the RF-identification (RFID) market appears strong with sales of $1.7 billion in 2004 projected to reach $5.9 billion in 2008. This upsurge in demand is driven by the promises of next-generation RFID systems, which vow to provide non-line-of-sight readability, improved security, and reconfigurable product information. Applications include inventory tracking, prescription medication tracking and authentication, secure automobile keys, and access control for secure facilities. Details of RFID applications and opportunities can be found in many previously published works.1-3 Such capability will be possible through the ultra-high-frequency (UHF) systems that are defined by the EPC-Global Class 1, Gen 2 (known in Europe and internationally as the ISO-18006 standard) protocols.4 They also will be enabled by innovations in tag/reader technology, such as the RF/analog and mixed-signal integrated-circuit (IC) designs being implemented through the latest CMOS process nodes. Many new IC requirements are being dictated by both the EPCGlobal Class 1, Gen 2 protocol and the design and simulation of several key radio blocks in a passive-backscatter UHF RFID tag circuit. Simulation tools can be used to investigate critical IC performance metrics for several worst-case system-level operating conditions.

The inductive-loop passive RFID systems, which operate at the low-frequency (LF) range of either 125 or 134 kHz or high-frequency (HF) allocation of 13.56 MHz, are limited to approximately 1 m of range. UHF RFID systems operate in the Industrial-Scientific-Medical (ISM) bands between 860 and 960 MHz and also at 2.4 GHz. They have a much longer reach with typical ranges of 3 to 10 m for a passive tag. That tag receives both information and operating energy from the reader's RF signal. If the transponder lies within the reader's range, an alternating RF voltage is induced on the transponder antenna. That voltage is rectified to provide a direct-current (DC) supply voltage for tag operation. The tag responds by modulating the impedance placed on the antenna terminals. In doing so, it backscatter's an information signal to the reader.

The reader sends information to one or more tags by modulating an RF carrier using double-sideband amplitude-shift-keying (DSB-ASK), single-sideband amplitude-shift-keying (SSB-ASK), or phase-reversal amplitude-shift-keying (PR-ASK) modulation at a bit rate ranging from 26.7 to 128 kb/s. Modulation is achieved using a pulse-interval-encoding (PIE) format. Here, data is passed to the tag by pulsing the carrier wave at differing time intervals to indicate a 0 or 1 b. Through frequency-band allocation and standardized data protocols, the EPC-Global initiative is designed to drop overall costs by unifying the disparate systems implemented around the world. The initiative will enable the use of relatively inexpensive CMOS technology to offset the costly development of designing new complex ICs.

The adoption of newer process nodes is expected to reduce IC size by 20 percent. Due to the quantities involved, the efforts to reduce system costs are particularly focused on the unit cost of the passive tag. They are targeting an order-of-magnitude cost reduction to just a few cents per tag.

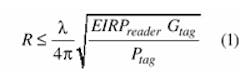

Passive-tag modulation differs from typical radio communications schemes in that the reader signal also powers the tag. In passive backscatter systems, the range is set by the forward link (reader-to-tag) through the radiated power available at the tag. The goal for the design of a modern Gen-2 tag is to maximize read range while providing full compliance with the protocol. The Range Equation (Eq. 1) determines the theoretical range in which the tag will receive adequate power levels to respond to the reader.5

where:

EIRP = the effective isotropic radiated power,

Ptag = the power required at the tag antenna output,

Gtag = the tag antenna gain, and

λ= the free-space wavelength of the RF carrier.

Turning off the reader power reduces the power that is available to the tag. The modulation schemes in which the signal is at its maximum value most of the time therefore have an advantage. Such modulation is spectrally inefficient, however. It leads to relatively wide channels or low data rates.

Per the EPC Class 1, Gen 2 specification, the reader transmits at powers up to 4 W EIRP. With a carrier frequency of 950 MHz, the channel loss would be 36.9 dB at a distance of 3 m. The power at the tag antenna would then be –0.88 dBm.

With this small amount of available power and low DC-power-conversion efficiency (rectifier efficiencies average around 20 percent), CMOS tag circuits typically operate on a single volt with only a few microamps of current. Given that passive RFID tags must be low in cost and power-thrifty, the tags are designed to receive signals from readers using relatively simple amplitude-modulation (AM) techniques. The analog front end of the UHF RFID tag contains several internal analog subblocks. That front end performs all of the analog processing for DC power, receive signal detection/demodulation, and transmit modulation. The block diagram in Fig. 1 shows the analog front end and digital state machine of a typical UHF RFID tag.

The rectifier converts the RF energy received by the antenna into DC power for all of the other blocks. That regulator is followed by a voltage regulator, which limits and regulates the voltage produced by the rectifier. The reset sub-block provides a reset signal indicating that the rectified voltage has reached a reliable, regulated level. For its part, the envelope detector detects and demodulates the reader data signal. It also produces the digital demodulated signal. A ring oscillator generates the clock for the digital state machine. The modulator places the modulated signal onto the tag antenna by alternating the load impedance on the antenna terminals. All analog front-end circuits were simulated using Ansoft's Nexxim circuit simulator using the Cadence Virtuoso design environment and the TSMC 0.18-µm standard CMOS process library.

To convert the extremely low input voltage up to a potential sufficient for operating CMOS circuits, the rectifier block in Fig. 2 uses a cascaded Dickson voltage multiplier circuit with multiple cascaded sections. The design is based on a four-stage charge pump using diode-connected, minimum-length PMOS transistors as rectifiers. The bulk terminals of those PMOS transistors were tied to the gate and drain terminals (back-bias) in order to reduce the effective threshold voltage. The transistor size and the value of the metal-insulator-metal (MIM) capacitors were obtained through optimization that directly used Nexxim's harmonic-balance simulations. The rectifier output goes directly into the voltage regulator.

Page Title

Voltage regulation is accomplished by using a voltage limiter followed by a regulator circuit. The limiter circuit ensures that the input voltage level to the voltage regulator is below the transistor 3.3-V breakdown voltage. The voltage regulator includes the startup and self-biased circuit, bandgap reference circuit, and voltage regulator. The regulator's output voltage level is set to 1.25 V, which will be the power-supply voltage level for the digital circuits and other analog circuits. Simulations revealed that the quiescent current consumption of the regulator is less than 200 nA. When the generated supply voltage from the charge-pump circuit is high enough, the reset signal goes to a "low" state to initiate state machine in the digital circuitry. To avoid false triggering, a reset circuit provides the necessary hysteresis characteristic.

DEMODULATOR AND RING OSCILLATOR

The demodulator is composed of a fast charge pump, peak detector, and comparator. The fast charge pump detects the ASKmodulated RF signal envelope. That envelope is further processed by the peak detector, which is formed by a diode-connected MOSFET and capacitor, to obtain its slow-moving average. The envelope signal and its slowing moving part are then compared to produce the demodulated signal in digital format. The comparator circuit shown in Fig. 3 is designed for rail-to-rail common-mode input range to accommodate a wide tag-operation range. Its hysteresis input-output characteristic also enables it to work under a noisy environment. The ring oscillator follows a report by Sundaresan, et al.6 Acting as the clock generator for the tag IC, the design provides a nominal oscillation frequency of 4 MHz. It is insensitive to both process and temperature variations.

The modulator modifies the capacitance of a varactor, which is connected to the antenna, according to the digital signal input. Varying the capacitance changes the antenna's radar cross section (RCS). The reader detects these variations so that the back-scattered information can be recovered on the reader side. The varactor is connected to the antenna terminals through the blocking capacitor. The voltage across the varactor is controlled by current biased inverted in the middle of Fig. 3. This current can slow down the speed of capacitance change so the back-scattered modulated signal can meet the FCC emission regulation.

The input impedance looking into the rectifier circuit is primarily capacitive. The antenna must be matched to this capacitive input to maximize the power absorbed by the rectifier from the incident wave. Because of the cost sensitivity, it is desirable to implement the impedance matching in the antenna itself rather than use discrete lumped elements. The goal of the antenna design is to adjust the antenna's dimensions so that its reactance resonates with the reactance of the chip input impedance. The antenna behavior was simulated using the planar method-of-moments electromagnetic field solver in Ansoft Designer.

Figure 4 is a plot of the input impedance of the tag front end. It is simulated with Nexxim's harmonic-balance engine under large signal conditions with source-impedance pulling. The optimal source impedance for power transferred into the tag circuit is Zs = 35 + j155 Ω at 900 MHz, which also is the desired input impedance when performing antenna design. Optimization was applied with the goal of achieving an input impedance of Zs so that the maximum power can be transferred from the source (or antenna). The final design, which is shown in Fig. 5, results in an input impedance of Za = 34.3 + j155 Ω with a flat impedance response across the entire UHF RFID band. It also boasts a broad omni-directional pattern with a gain of 1.95 dB.

After all of the necessary circuits and the antenna have been designed, it is worthwhile to put all of the blocks together in the system simulator to perform communication link analysis. Two separate system benches were implemented in Ansoft Designer for performing the link test. The reader-to-tag (i.e., uplink test) and tag-to-reader (i.e., downlink test) test bench are shown in Fig. 6. The reader is implemented using behavioral models in both cases. For tag-to-reader testing, the behavioral PSK demodulator on the reader side is also included to recover the PSK backscattered modulated signal.

The EPCglobal protocol provides a long continuous-wave (CW) burst to allow tag power-up prior to sending data. The following simulation results show the power-up behavior during that period of leading CW radiation (Fig. 7). The supply voltage ripple can be observed under the condition of deep amplitude modulation (AM). The recovered PIE waveform is shown in green in Fig. 8.

Figure 9 shows back-modulated data as input on the tag side. As mentioned earlier, the reader experiences back-scattered energy through an RCS change. Although the data recovery can be seen on the reader side, it is a bit noisy. The recovered timing and pulse period is well correlated to the modulated signal's input.

The circuit design for the EPC Global, Class-1, Generation-2 UHF RFID tag presented here was based on a commercial 0.18-µm CMOS process. The designs and simulations for the tag's analog front end, which included the rectifier, voltage regulator, reset, demodulator, and modulator circuits, were illustrated using standard foundry library components and an established IC design flow. Nexxim was used to introduce additional harmonic-balance and sourcepull simulations. The antenna design shown here provides conjugate match with the input impedance of the rectifier. To bring all of these aspects together, top-level verification combines behavioral modeling, HFSS antenna system modeling, and Nexxim transient simulation. In doing so, it shows that the design provides reliable DC power and demodulated signals for both uplink and downlink. See Figure 10.

REFERENCES

- J. Landt, "The History of RFID," IEEE Potentials, Vol. 24, No. 4, Oct.-Nov. 2005, pp. 8-11.

- R. Glidden, et al., "Design of Ultra-Low-Cost UHF RFID Tags for Supply Chain Applications," IEEE Communications Magazine, pp. 140–151, Aug. 2004.

- U. Karthaus and M. Fischer, "Fully Integrated Passive UHF RFID Transponder IC With 16.7-�W Minimum RF Input Power," IEEE Journal of Solid-State Circuits, Vol. 38, No. 10, pp. 1602 – 1608.

- "EPC™ Radio-Frequency Identity Protocols Class-1 Generation-2 UHF RFID Protocol for Communications at 860 MHz-960 MHz Version 1.0.9," http://www.epcglobalinc.org/standards/

- B. Sklar, Digital Communications Fundamentals and Applications, pp. 195, Prentice Hall, 1988.

- K. Sundaresan, P.E. Allen, and F. Ayazi, "Process and Temperature Compensation in a 7-MHz CMOS Clock Oscillator," IEEE Journal of Solid-State Circuits, Vol. 41, No. 2, pp. 433-442, Feb. 2006.