Hybrid VCO Enables Robust Startup

To enable higher-frequency and lower-power circuitry for high-data-rate wireless communications, advancing RF integrated-circuit (IC) technology is critical. Using CMOS technology offers the benefits of low voltage, low direct-current (DC) dissipation, and high integration of deep-sub-micrometer-range processes. Such advantages can be leveraged to create advanced circuits at a fraction of the current power draw. Using this knowledge, To-Po Wang and Yaon-Ming Yan from China’s National Taipei University of Technology have designed a VCO circuit with a measured tuning range of 25.6%.

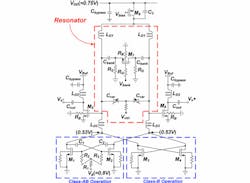

To solve a traditional problem of high-performance class-B VCOs, a hybrid-class AB/B VCO typology can be used to soften startup conditions. This approach lowers the DC dissipation of the circuit using a 0.18-μm CMOS process. The sweep frequency of the VCO ranges from 10.10 to 13.15 GHz.

The hybrid VCO requires 2.4 mW of power with a supply voltage of 0.75 V. Phase noise in the bias condition for all frequencies averages -101.4 dBc/Hz at 1 MHz offset from the carrier. Such low phase noise is achieved by using a pMOS transistor as a tail current driver. High-value resistors (5 kμ) are implemented at the gate and bank bias voltages. See “A Low-Voltage Low-Power Wide-Tuning-Range Hybrid Class-AB/Class-B VCO with Robust Start-Up and High-Performance FOM_T,” IEEE Transactions on Microwave Theory and Techniques, March 2014, p. 521.

About the Author

Jean-Jacques DeLisle

Jean-Jacques graduated from the Rochester Institute of Technology, where he completed his Master of Science in Electrical Engineering. In his studies, Jean-Jacques focused on Control Systems Design, Mixed-Signal IC Design, and RF Design. His research focus was in smart-sensor platform design for RF connector applications for the telecommunications industry. During his research, Jean-Jacques developed a passion for the field of RF/microwaves and expanded his knowledge by doing R&D for the telecommunications industry.