The design of phase-locked microwave sources typically involves one of two approaches: direct synthesis or indirect synthesis. Direct synthesis uses a very stable reference source, such as a temperature-compensated crystal oscillator (TCXO) or oven-controlled crystal oscillator (OCXO), and multiplies up to the desired frequency. With indirect synthesis, a coupled portion of the voltage-controlled oscillator’s (VCO) output is fed back and its frequency is divided to match that of a stable reference source.

This article discusses the benefits and pitfalls of each method, and explains how they affect the overall phase noise. For instance, when close-to-carrier phase noise is critical, direct synthesis is often the favored approach.

Radical changes have occurred in the design and manufacturing methods of phase-locked RF sources, thanks to advances in programmable phase-locked loops (PLLs) and integrated PLL/VCOs that now enable a more flexible and cost-effective approach. The phase noise of these integrated devices is also comparable to that of discrete devices used with traditional methods. For example, a phase noise of ‒100 dBc at 100-kHz offset—across a 20-GHz bandwidth—is achievable.

Indirect Synthesis

Indirect synthesis, also commonly known as the PLL approach, couples off a portion of an RF oscillator’s (e.g., VCO) output and divides its frequency to precisely match that of a stable reference source (such as a TCXO). If the frequency of the fed-back signal is ever-so slightly different than that of the reference source, the phase frequency detector (PFD) generates an error signal, which then retunes the frequency of the VCO to the correct value. This continuous feedback arrangement ensures that the error signal is always zero and the frequency is therefore locked at a fixed frequency.

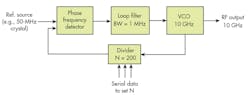

1. Shown is a phase-locked-loop (PLL) block diagram.

Figure 1 shows an example where an X-band microwave source at 10 GHz requires a divider of exactly 200 to be matched to a 50-MHz reference. In this example, a programmable divider is used because it provides the flexibility of output frequency selection.

Traditionally, before programmable devices, fixed frequency sources were commonly used. This was particularly the case in military applications, such as local-oscillator (LO) sources in up/down converter modules. These applications would use a fixed frequency divider.

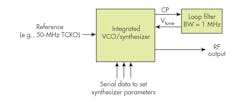

Nowadays, both the PFD and the programmable frequency divider are integrated into a single PLL monolithic microwave integrated circuit (MMIC). Recent synthesizer developments have enabled very precise frequency selection and fine steps (e.g., 1 Hz). Synthesizer technology has progressed further to include the VCO in the MMIC (Fig. 2). The external components required are a stable reference source (e.g., a TCXO), a carefully designed loop filter, regulated power supplies, and a means of programming or interfacing with the synthesizer.

2. This figure illustrates an integrated PLL/VCO.

In addition, synthesized frequencies of up to 20 GHz can be generated with very low phase noise (e.g., ‒100 dBc at 100-kHz offset) with these new packaged PLLs. As a result, they are well-suited for either commercial or military applications. The other advantages of MMIC-based synthesizers include added flexibility for a variety of applications, lower-cost materials/products, and reduced production time.

Many PLL/synthesizer MMIC devices contain volatile memory, since they are devoid of EPROMs. Information is sent via serial peripheral interface (SPI) to the synthesizer chip, which sets a variety of control parameters—such as the number of frequency divisions. The output frequencies of the synthesizer are phase-locked to precise values within the frequency range of the VCO. All of this required data can be programmed onto an EPROM chip so that the SPI data is triggered and sent to the PLL/synthesizer chip as the unit powers up.

To improve the noise performance of an N-integer PLL, it is desirable to minimize the N counter value and maximize the phase detector frequency, fpd. If N is an integer, the maximum value of the phase detector frequency is limited to the size of the channel spacing, Δf.

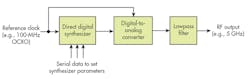

3. Shown is a representation of direct digital synthesis.

If N is a fractional value, Δf can be further reduced, improving the frequency resolution. Fractional–N synthesizers can also have very low phase noise with very fast switching speeds. In the past, their drawback has been fractional spurs, but today, methods such as analog compensation are able to suppress them.1 For high-frequency applications with low channel spacing, fractional-PLL synthesizers are the preferred option.2

Direct Digital Synthesizers

Major developments of late in direct-digital-synthesizer (DDS) technology have led to significant performance improvements. DDS requires a digital-to-analog converter and a lowpass filter to remove the unwanted products and harmonics of the output signal (Fig. 3). This can often be complex to set up and a problematic option if spurious emissions are undesirable.

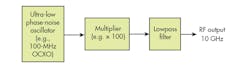

4. This image depicts an OCXO being multiplied up to a higher frequency.

However, it’s possible to achieve fine frequency steps, making the close-to-carrier phase noise more desirable in comparison to indirect synthesis. A simpler but less flexible method that has the same benefits and pitfalls as DDS is to multiply a very clean crystal source, such as an OCXO (Fig. 4).

Phase-Noise Performance

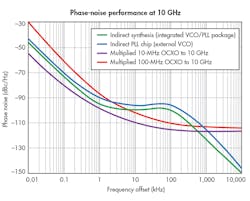

Figure 5 shows the phase-noise performance of direct synthesis by multiplication compared with the indirect (PLL) method. The chart reveals that improved phase noise is achieved by multiplying the 10-MHz OCXO—currently available 10-MHz OCXOs feature ultra-high stability.

5. These plots compare phase noise performance of direct and indirect synthesis.

The graph also shows that the direct multiplication method can attain lower phase noise than PLL methods at close-to-carrier offset frequencies up to 500 kHz. At offsets greater than 500 kHz, the phase noise of the VCO dominates in the PLL method. This results in lower phase noise for the PLL technique at these larger offset frequencies.

Design and Manufacturing

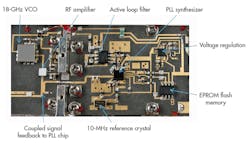

Figure 6 shows a PLL/VCO board designed and manufactured at Specialist Microwave Solutions Ltd., U.K. The unit outputs a fixed-frequency phase-locked signal from an amplified VCO (left-hand side of the figure). Some of this signal is fed back to a PLL device, which divides the 18-GHz signal down to be compared with that of a clean 10-MHz reference source (courtesy of a PFD).

6. Shown is the board layout of a PLL/VCO-based design.

The correction signal generated from the PLL device then passes through an active loop filter back to the tuning port of the VCO to ensure that the VCO’s output is continuously locked at a predefined frequency. This circuit shows a phase-locked 18-GHz source. However, the circuit can be adapted to output a wide range of phased-locked frequencies by changing the VCO, loop filter components, and software instructions. Low phase-noise frequency synthesizers that can output many frequency channels across a predefined bandwidth are also designed and manufactured at Specialist Microwave Solutions Ltd.

Conclusion

The development of programmable PLLs and integrated synthesizer chips provide a flexible and cost-effective approach to the design of a frequency source. Comparing the phase-noise performance of some of these approaches can help pinpoint the best solution for your design. The methods discussed here include utilizing a PLL synthesizer chip along with an external VCO; using an integrated PLL/VCO; and direct multiplication.

The first approach mentioned above can offer added flexibility, as it can be used to phase-lock a range of VCOs, dielectric-resonator oscillators (DROs), etc. Recent advances of integrated synthesizer MMICs have resulted in phase-noise performance that meets commercial and military specifications. Whenever a new requirement for a microwave source arises, the final decision on the appropriate design approach will be based on a range of specifications, such as the allocated cost, size, frequency resolution, and phase noise.

References

1. Banerjee, Dean, PLL Performance, Simulation and Design, Fourth Edition, Dog Ear Publishing, 2006.

2. Texas Instruments, AN-1879 Fractional N Frequency Synthesis, Application Report SNAA062A, Revised April 2013.