Fei Yu and Chunhua Wang

Millimeter-wave communications systems rely on affordable amplification with high signal gain and low noise figure. By designing a fully integrated differential low-noise amplifier (LNA) with an interstage LC parallel tank circuit with common-gate (CG) and common-source (CS) transistors, this amplifier achieves image-rejection ratio (IRR) of 80 dB at 70 GHz. It also features a capacitor cross-coupled transconductance (gm) boosting scheme to further improve gain and noise-figure performance. The two-stage, current-reuse LNA, which is ideally suited for use in the 64-GHz band, is based on a standard 0.18-m CMOS process. It consumes 34.3 mW from a +1-VDC supply and achieves peak gain of 23.8 dB and minimum noise figure of 3 dB with -3.8 dBm output power.

High-data-rate millimeter-wave wireless systems have attracted tremendous attention in recent years. Much effort has been carried out in order to develop millimeter-wave circuits for wireless communication systems for the unlicensed band around 60 GHz (about 9 GHz of bandwidth).1,2 With the advances in device fabrication technology, transistors with cutoff frequencies (ft) and maximum oscillation frequencies (fmax) beyond 100 GHz have been commercially available in deep-submicrometer CMOS processes, motivating RF integrated-circuit (IC) designers to reach for higher frequencies.3 These advantages make a 60-GHz CMOS transceiver a possibility with high integration and low cost.4 However, problems with signal images must still be addressed at these frequencies. Since millimeter-wave technology has extended beyond usable frequencies to 70 GHz, image or interference signals in the 60-GHz band may be at higher levels that the desired communications signals (Fig. 1). In addition, a bandpass filter is usually needed after a 60-GHz receiver's low-noise amplifier (LNA) to remove unwanted jamming signals that may arise from some automotive radar applications.

To minimize cost and size, monolithic integration of the LNA with an image-reject (IR) bandpass filter (Fig. 2) is necessary. Due to the low quality factor (Q) of on chip inductors, pre-filtering and IR-filtering are generally accomplished by means of external passive filters.5 These external filters are large and expensive. To eliminate the need for these external filters, some successful LNA designs have focused on the development of a monolithic IR filter using a notch filter.5-8 But the operating frequency of such LNAs is well below 60 GHz.

Recently, numerous LNAs fabricated with CMOS processes were reported at 60 GHz. For example, a traveling-wave amplifier in 90-nm silicon-on-insulator (SOI) CMOS technology was presented in ref. 9 with 9.7-dB small-signal gain. A millimeter-wave LNA in 65-nm CMOS was presented in ref. 10 with a power gain of 8.4 dB and noise figure (NF) of 5.5 dB at 61 GHz. A 60-GHz LNA based on a 130-nm CMOS process was reported with 20.4-dB small-signal gain and 8.7-dB NF in ref. 11. In ref. 12, a 64-GHz amplifier based on a 90-nm CMOS process was reported with 15.5-dB peak gain and 6.5-dB NF. From refs. 9-12, it can be seen that standard bulk CMOS has a potential for millimeter-wave wireless applications. But the gain levels of these LNAs are low (less than 20 dB) and their noise figures relatively high (greater than 5.0 dB). Also, there was no IR capability to suppress unwanted interference.

This report describes a high-gain, low-power CG-LNA based on standard 0.18-m CMOS technology. The LC parallel tank combined with the cascode stage forms a bandstop filter to reject interference. A gm-boosted technique is applied to increase gain and reduce noise figure. The proposed IR-LNA was optimized for millimeter-wave applications at 64 GHz and image signals at 70 GHz. A two-stage fully integrated differential topology was adopted in this design. The amplifier achieves peak gain of greater than 23.8 dB, with noise figure of less than 3.0 dB and IRR of greater than 80 dB, exhibiting excellent RF performance at low supply voltage and power consumption.

The most widely studied millimeter-wave LNA design approaches lately have been common-source low-noise-amplifier (CS-LNA) architectures with inductive degeneration and common-gate low-noise-amplifier (CG-LNA) architectures (Fig. 3). The CS-LNA provides both high gain and relatively low noise for the narrow band application. However, for millimeter-wave applications, it is preferable to use a CG-LNA topology for its lower power consumption, wideband input matching, lower sensitivity to parasitic, and better reverse isolation.13

Page Title

From Fig. 3(a), the input impedance can be expressed as shown in Eq. 1:

Zin,CS-LNA(ω) ≈ (1/jωC1) + (1/jωC2) mLs/Cgs) + (1/jωCgs) + jωLs>(1)

where:

gm = the transconductance and

Cgs = the gate-source capacitance of transistor M.

Its minimum noise factor including channel thermal noise and induced gate noise is reduced to Fmin,C,S-LNA as shown in Eqs. 2 and 314:

Fmin,C,S-LNA ≈ 1 + (δ/α) + (ω0/ωT)(2δαa2/5γ)Qopt)(2)

Qopt = )0.5 + (5γ/δ&alpha)0.5(3)

where:

ωT = gm/Cgs = the unity current gain frωquency of M;

α, δ, and γ = process- and bias-dependent variables;

c = the correlation coefficient between the gate noise and drain noise of M; and

ω0 = the operating frequency.

From Fig. 3(b), the input impedance of the CG-LNA can be found from Eq. 4:

Yin,CG-LNA (ω) ≈ jωC12 + Cgs) + 1/jωLS>(4)

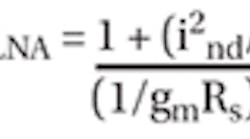

Usually, induced gate noise is negligible in a CG-LNA circuit. So, the noise factor is given by Eq. 515:

where:

i2nd = 4kTγgd0Δf;

i2ns = 4kTRS-1gd0Δf; and RS = the source resistance.

When gmRS ≈ 1, Eq. 5 reduces to Eq. 6:

Fmin, CG-LNA ≈ 1 + γ/α(6)

To alleviate the higher noise figure in the CG-LNA, an inverting gain stage is inserted between the gate and source terminals (Fig. 4). With negative feedback, the effective transconductance of M is boosted to (1 + A)gm. Using the new input matching condition, (1 + A)gmRS = 1, the noise factor is reduced to the amount shown in Eq. 713-15:

FCG-LNA ≈ 1 + (7)

In the gm-boosted CG-LNA, the resistive input impedance consumes less bias current resulting in less channel noise from the input transistor and a correspondingly smaller noise contribution and lower power consumption.15 One possible way to implement the inverting amplification is by means of a capacitor cross-coupled CG-LNA (Fig. 5), where the inversion is naturally available in a differential configuration.

Page Title

From Fig. 5, the inverting gain, A, is given by Eq. 8:

A(Ω) = jΩRC/(1 + jωRC)(8)

where:

C = Cc/(Cc + Cgs);

Cc = the coupling capacitor; and

R = the bias resistor.

As a consequence, the effective transconductance can be expressed by Eq. 9:

Gm(Ω) = gm = gm(9)

and the noise factor by Eq. 10:

F'CG-LNA(Ω) ≈ 1 + Γ/α 1 + (Γ/α)(10)

In this design, the bias resistor R is around 5 kΩ. When Cc ? Cgs, the result is C 1 and A(Ω) 1, then

Gm 2gm(11)

FCG-LNA 1 + Γ/2α (12)

Finally, the effective input transconductance is doubled and the noise factor is decreased. The simulated gain and noise-figure results with and without Cc are shown in Fig. 6. The results with Cc have higher gain and lower noise figure compared to those without Cc, verifying the correctness of the theoretical analysis.

Because of the available bandwidth, the design of millimeter-wave transceivers has received a great deal of attention in recent years. But IRR is critical in these transceivers, typically achieved by the use of off-chip filters which raise the cost of the transceiver. Ideally, improved signal-image rejection can be achieved by means of an on-chip IC as part of the LNA. An on-chip IR-LNA with third-order active notch filter at 2.4 GHz was introduced in ref. 6 Fig. 7(a)>. Through a small-signal equivalent circuit of the filter analysis, the filter input impedance, Zin,filter, and the filter's frequency of resonance, fim, can be found by Eqs. 13 and 14, respectively6:

Zin,filter = 1/jΩCf Z1(13)

fim = 1/gsCf)/(Cgs + Cf)>0.5(14)

where:

Z1 = jΩLf + 1/jΩgs) + (1/Cf)> (gm/Ω2CgsCf)(15)

The parasitic resistances of the inductor and transistor have been neglected here. By using this notch filter, the image signal is extracted from the original signal path while the wanted signal is not extracted. In other words, the image signal is suppressed while the wanted signal is not degraded.6 However, the input impedance of the notch filter may be lower than the case of the LNA without the filter at the desired frequency; some desired signals may be lost to ground due to the filter,7 and the gain and noise-figure performance of the amplifier may be deteriorated by the filter.

To overcome these issues, an improved IR-LNA with third-order active notch filter at 5.25 GHz was developed Fig. 7(b)>.7 A feedback connection from the drain of transistor M to point A was added. Using the small-signal equivalent circuit of the filter, the input impedance can be re-expressed as:

Zin, filter = Zin,filter/(1 + gm/ΩCgs)(16)

From Eq. 16, the input impedance decreased by a factor of 1 + gm/ΩCgs, such that the impedance difference is less dependent on the negative term in Eq. 15, and the power gain and noise figure performance of the amplifier are not made worse. This analysis indicates that the common-source (CS) structure is sensitive to source and gate device parasitic capacitance , and a cascaded CS IR-LNA would be difficult to design for use above 10 GHz. For this reason, most millimeter-wave IR-LNAs adopt a CG structure with a passive notch filter.

Page Title

In the CG approach, a CG-LNA with passive notch filter and current reuse was introduced in ref. 5 (Fig. 8). A simple interstage LC parallel tank was interconnected with CG and CS transistors. From Fig. 8, the input impedance of the LC notch- filter is given by Eq. 17:

ZSB,filter (ω) = (jωLe)/(1 ω2LeCvar)(17)

The image and desired signals can be found from Eqs. 18 and 19:

fSB,im = 1/eCvar)0.5>(18)

fPB,im = 1/{2π e(Cvar + Cgd1 + Cgd2)>0.5}(19)

where:

Cgd1 = the gate-drain capacitance of device M1 and

Cgd2 = the gate-source capacitance of device M2.

From Eqs. 18 and 19, it can be seen that the notch filter provides a low impedance at the image frequency and high impedance at the desired frequency. In addition, the filter can remove the effects of the parasitic capacitance in the signal path of the cascode amplifier. Thus, the filter can archive good noise performance and high IIR at the same time.7 The IIR can be approximated by Eq. 20:

IIR = 20log(GPB/GSB)(20)

where:

GPB = the gain of the passband and

GSB = the gain of the stopband.

From Eq. 18, the filter notch frequency can be tunable by the use of varactors Cvar. By tuning various parameters, it is possible to control the resonance frequency. Figure 9 and Figure 10 show gain and noise-figure characteristics with different values of Cvar. When Cvar is increased from 275 to 295 fF, the resonant frequency decreases from 71 to 69 GHz, and the gain exhibits about a 1.2-dB variation. The IIR value is a maximum when Cvar = 285 fF. The noise figure exhibits about a 1.5-dB variation. The rejection frequency can be varied in the range 1.07fRF to 1.1fRF with only a slight influence on the passband gain and noise figure.

A detailed schematic of the gm-boosted and high IR LNA comprising two cascaded amplifiers is shown in Fig. 11. The preamplifier consists of the capacitor cross-coupled gm-boosted stage, the LC parallel resonant network and CS stage, and the post-amplifier with two CS stages and output matching network, both of which adopt the current-reuse scheme for minimal power consumption.

In the pre-amplifying stage, the gain is enhanced via capacitor cross-coupled technique and peaking-inductor (Lp) technique in the differential configuration, wherein inductor Ls resonates with the input node capacitance at the operating frequency. The output noise is reduced by the gm-boosted technique also. The LC parallel tank forms a bandstop filter to reject interference at fim. Therefore, the resulting circuit provides bandpass gain, peaking at fRF. The post-amplifier employs a common-source gain stage cascaded with a current-reused differential pair. Inductor Li is designed for interstage impedance matching. Inductors Lo1 and Lo2 and capacitor C4 implement the T-section matching to a 50-Ω load for the output stage. All capacitances are implemented with metal-insulator-metal (MIM) capacitors and all 5-kΩ gate bias resistors were realized using n+ poly resistors. The IR-LNA's circuit parameters are summarized in Table 1.

To demonstrate the effectiveness of the design approach, a 64 GHz IR-LNA was implemented using the standard 0.18-m CMOS process from TSMC. The circuit draws only 34.3 mA from a 1-V supply. All results were obtained by the post-layout simulation. The gain and noise figure performances as functions of frequency can be seen in Fig. 12. The small signal gain has a peak of 23.8 dB at 64 GHz with 80 dB IIR due to a transmission zero is generated at 70 GHz. The noise figure has a minimum of 3.0 dB at 64 GHz. The input and output return losses are presented in Fig. 13. The minimum input and output return losses are 14.4 dB and 13.7 dB, respectively. At 1 V bias condition, the output-referred 1-dB compression point (P1dB_out) at 64 GHz is -3.8 dBm.

The performance of the proposed IR-LNA is summarized in Table 2 and compared with the state-of-art LNA designs with and without notch filters. As can be seen from Table 2, the proposed IR-LNA has good gain and noise figure as well as low power consumption. Compared to LNAs in refs. 5-8, the current IR-LNA design has better IRR of 80 dB. The comparison results show that this IR-LNA, implemented by integrating passive notch filters with the proposed gm-boosted technique, shows good improvement in the gain and NF.

In short, a gm-boosting technique was applied to a standard 0.18-m CMOS process to improve gain and noise figure while reducing power consumption for a CG-LNA. With the help of a capacitor cross-coupled technique, the fully integrated differential LNA consumes only 34.3 mA from a 1-V supply while attaining a gain of 23.8 dB and minimum noise figure of 3 dB at 64 GHz. By using high image rejection notch filters, the LNA provides an excellent IRR of 80 dB without external components. The LNA is suitable for millimeter-wave transceivers at 60 GHz where high gain and high image rejection are required.

FEI YU, Doctor

CHUNHUA WANG, Professor

College of Information Science and Engineering

Hunan University

Changsha 410082

People's Republic of China

e-mail (Fei Yu): [email protected]

e-mail (Chunhua Wang): [email protected]

References

- B. Razavi, "A 60-GHz CMOS Receiver Front-End," IEEE Journal of Solid-State Circuits, Vol. 41, No. 1, January 2006, pp. 17-22.

- D. Dawn, P. Sen, S. Sarkar, et al., "60-GHz Integrated Transmitter Development in 90-nm CMOS," IEEE Transactions on Microwave Theory and Techniques, Vol. 57, No. 10, October 2009, pp. 2354-2367.

- H.-H. Hsieh and L.-H. Lu, "A 40-GHz Low-Noise Amplifier With a Positive-Feedback Network in 0.18-m CMOS," IEEE Transactions on Microwave Theory and Techniques, Vol. 57, No. 8, August 2009, pp. 1895-1902.

- A. Parsa and B. Razavi, "A New Transceiver Architecture for the 60-GHz Band," IEEE Journal of Solid-State Circuits, Vol. 44, No. 3, March 2009, pp. 751-762.

- W.-L. Chen, S.-F. Chang, G.-W. Huang, et al., "A Ku-Band Interference-Rejection CMOS Low-Noise Amplifier Using Current-Reused Stacked Common-Gate Topology," IEEE Microwave and Wireless Components Letters, Vol. 17, No. 10, October 2007, pp. 718-720.

- T.-K. Nguyen, S.-K. Han, and S.-G. Lee, "Ultra-low-power 2.4 GHz image-rejection low-noise amplifier," Electronics Letters, Vol. 41, No. 15, July 2005, pp. 842-843.

- T.-K. Nguyen, N.-J. Oh, C.-Y. Cha, et al., "Image-rejection CMOS low-noise amplifier design optimization techniques," IEEE Transactions on Microwave Theory and Techniques, Vol. 53, No. 2, February 2005, pp. 538-547.

- D. Ma and F.F. Dai, "A 7.27 GHz Q-Enhanced Low Noise Amplifier RFIC With 70 dB Image Rejection Ratio," IEEE Microwave and Wireless Components Letters, Vol. 20, No. 8, August 2010, pp. 456-458.

- F. Ellinger, "60-GHz SOI CMOS traveling-wave amplifier with NF below 3.8 dB from 0.1 to 40 GHz," IEEE Journal of Solid-State Circuits, Vol. 40, No. 2, February 2005, pp. 553-558.

- Y. Yikun, P.G.M. Baltus, and A. De Graauw, et al., "A 60 GHz Phase Shifter Integrated With LNA and PA in 65 nm CMOS for Phased Array Systems," IEEE Journal of Solid-State Circuits, Vol. 45, No. 9, September 2010, pp. 1697-1709.

- B.-J. Huang, C.-H. Wang, C.-C. Chen, et al., "Design and Analysis for a 60-GHz Low-Noise Amplifier With RF ESD Protection," IEEE Transactions on Microwave Theory and Techniques, Vol. 57, No. 2, February 2009, pp. 298-305.

- 0.S. Pellerano, Y. Palaskas, and K. Soumyanath, "A 64 GHz LNA With 15.5 dB Gain and 6.5 dB NF in 90 nm CMOS," IEEE Journal of Solid-State Circuits, Vol. 43, No. 7, July 2008, pp. 1542-1552.

- C.-S. Wang, J.-W. Huang, K.-D. Chu, et al., "A 60-GHz Phased Array Receiver Front-End in 0.13-m CMOS Technology," IEEE Transactions on Circuits and Systems I: Regular Papers, Vol. 56, No. 10, October 2009, pp. 2341-2352.

- W. Zhuo, X. Li, S. Shekhar, et al., "A capacitor cross-coupled common-gate low-noise amplifier," IEEE Transactions on Circuits and Systems II: Express Briefs, Vol. 52, No. 12, December 2005, pp. 875-879.

- L. Xiaoyong, S. Shekhar, and D.J. Allstot, "Gm-boosted common-gate LNA and differential colpitts VCO/QVCO in 0.18-m CMOS," IEEE Journal of Solid-State Circuits, Vol. 40, No. 12, December 2005, pp. 2609-2619.