Phase locked loops (PLLs) are common to many communications systems, including in WiMAX Access Points (AP). By performing an analysis of the phase-noise contributions of the PLLs within a WiMAX AP frequency chain, which is essentially the string of PLLs in the system starting with the frequency reference in the controller and ending with the transmitter local oscillator (LO) in the RF head, it is possible to better understand the impact that each PLL has on overall system performance.

Figure 1 provides a block diagram for a hypothetical frequency chain in a WiMAX AP. Each box in the block diagram represents a PLL that serves a unique purpose in the AP design. Since all the PLLs are connected in series, the signal and noise at the output of each PLL feeds the input port of the next PLL in the chain. All seven PLLs in this example contribute to the ultimate signal and noise performance at the output of the chain. For practical analysis purposes, the chain begins with the reference oscillator in the site controller. This special loop is locked to the Global Positioning System (GPS) receiver, but the loop bandwidth is so low that the only noise at the site controller reference PLL's output is the phase noise of the oven-controlled crystal oscillator (OCXO).

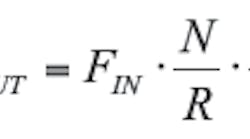

To review the essentials of PLL design,1-3 a PLL is a control loop that typically locks the phase and frequency of a tunable signal source, such as a voltage-controlled oscillator (VCO), at the output of the loop to the frequency and phase of a presumably stable signal at the input of the loop. Figure 2 shows the major elements of a PLL. The frequency of the loop output (FOUT) is related to the frequency at the loop input (FIN) by

where

N = the loop frequency multiplication factor,

R = the reference oscillator divider, and

P = the output divider, which is optional.

Designing for a higher-than-needed frequency and then dividing the output to reach the desired frequency is an approach that can be used to improve noise performance. Post-loop frequency division can also be used to lower the output frequency that is sometimes needed by the reference divider of a subsequent stage. Most, if not all, PLLs act as phase-noise filters to the input signal (with each PLL exhibiting a unique lowpass response) and also as phase-noise generators. Some important points to note about PLL noise theory are that:

1. Each PLL has a unique lowpass response, most often characterized by the closed-loop 3-dB banwidth.

2. At frequencies above the loop bandwidth, the loop attenuates the phase noise of the input signal and also attenuates the phase noise of the phase detector and charge pump inside the loop.

3. At frequencies below the loop bandwidth, the loop attenuates the phase noise of the VCO or other voltage-controlled element in the loop.

The choice of loop bandwidth is often based upon achieving optimal noise at the loop output. Most often this is the point where the curve of the multiplied reference noise and the PLL noise floor crosses the curve for the free-running VCO's noise on a phase-noise-versus-frequency plot. At other times, this noise-optimal bandwidth must be compromised in order to meet loop lock-time requirements. Charge pump settings, choice of dividers, and loop filter components are chosen to design a particular loop bandwidth while meeting noise, lock-time, and stability requirements. This design process is well understood, and many software programs are available from PLL IC suppliers to aid in PLL design.4,5

Design parameters chosen for each PLL can be entered into commercial computer-aided-engineering (CAE) software, such as the Advanced Design System (ADS) software from Agilent Technologies, to verify loop response (bandwidth and stability).6 This should be done for each PLL in the frequency chain. Figure 3 shows an example simulation model for a 50 MHz RF head reference PLL, while Fig. 4 shows example simulation output results.

Simulation results show that this loop has reasonable stability, evidenced by the low gain peaking shown by marker 1 on the red curve in in Fig. 4 (less than 2 dB) and the phase margin result of 48.2 deg. Phase margin of 45 deg. or higher is considered stable for most designs. Furthermore, the simulation result shows that the loop's 3-dB closed-loop bandwidth is around 26 Hz. This was purposely designed to be quite low in order to filter out nearly all of the incoming phase noise on the reference source. To validate simulations, measured data for closed-loop responses should be compared with the simulation results for each PLL in the chain. Accurate simulations of loop response and stability are essential for achieving accurate cascaded loop response simulations (which include the phase noise of all PLLs in the chain).

Armed with the design parameters for each PLL, a commercial CAE program can also be used to verify output phase noise. This should also be done for each PLL in the frequency chain. An example simulation model is shown in Figs. 5 and 6 along with example simulation output results in Fig. 7.

The simulation file shown in Figs 5 references a simulation schematic (called Ref_Synth_50 MHz in Fig. 5, and fully expanded in Fig. 6). This is controlled by the AC controller AC1 in Fig. 5. Designing simulations in this modular fashion allows PLL modules to be designed that can be used in other simulations. These simulations are behavioral in nature rather than at the circuit level, but they are valuable for predicting PLL behavior. As with all simulations, the validity of the output depends on the accuracy of the inputs.

Continue to page 2

Page Title

Accurate simulations must include all loop parameters, such as VCO tuning constant, charge pump current, loop filter components, and divider values. In addition, a piece-wise linear model of input reference phase noise, free-running VCO noise (or actual phase-noise data), and values for PLL integrated-circuit (IC) noise floor, charge pump noise, and divider noise floors must be estimated. The results shown in Fig. 7 include noise contributions from the voltage-controlled crystal oscillator (VCXO) in the loop, the reference noise, and the phase detector noise. The results shown in Fig. 8 show the same noise contributors after modification by the loop response.

Once hardware is available, it is essential to verify simulation results against measured data. Depending on the simulation tool used, certain parameters, such as charge pump noise contribution, may need to be adjusted. Each PLL in the frequency chain should be simulated in this way (once for stability and response, and once for phase noise) before moving on to simulate the phase noise of the total frequency chain.

Before moving on to discuss the simulation of all the PLLs in series, it might be helpful to review the function of each PLL in the chain of Fig. 1, and estimate the impact it has on the total system phase noise.

The first PLL in the chain (PLL 1) is the site controller reference loop (10 MHz in this example). It is used to lock a low noise TCXO or OCXO to a GPS reference. This loop is often designed for an extremely low loop bandwidth, such as 0.1 or 0.01 Hz. This implies a lock time on the order of several minutes. For all practical purposes, the output noise of this loop is the same as the free-running phase noise of the TCXO or OCXO under loop control. As will be seen, the very close-in noise (from 1 to 10 Hz, for example) of this PLL often continues to dominate all the way through the system.

The second PLL (PLL 2) is the model of a low-frequency system clock (200 MHz in this example. It is locked to the site controller reference, and is often an integer multiple of the system's symbol rate. In this example, the loop bandwidth of this PLL is about 75 Hz. Its far-out noise requirements are generally not as critical as those of other PLLs, but designers must take care that this loop does not add significant phase noise to the system, especially in the 1-to-100-Hz-offset regions. High noise in this region can degrade transmitter frequency error.

The third PLL (PLL 3) is the modem Serializer/Deserializer (SerDes) clock generator (3 GHz in this example). This PLL accepts the modem low-frequency clock signal at its input and generates very high-speed serial clock signals. These are often embedded with baseband and control data onto a fiber-optic link to the WiMAX system's RF head. These PLLs usually have very wide loop bandwidths, on the order of several hundred kilohertz, and even up to a few megahertz. They pass all the close-in phase noise of their references, and don't have particularly good phase noise far out compared to an RF PLL. The higher far-out noise is usually filtered by PLLs further down the transmitter frequency chain.

The fourth PLL (PLL 4) is the RF head SerDes clock recovery PLL. It is similar to PLL 3, except it is used to recover the low-frequency system clock from the SerDes link. The output of this PLL in the example system is a recovered 200-MHz low-frequency system clock. This loop also has a very wide loop bandwidth and therefore it passes the close-in noise of its reference. It also doesn't have particularly good phase noise at far-out offsets. Again, the higher far-out noise is usually filtered by PLLs further down the transmitter frequency chain. The output of this loop may be externally divided before passing the signal on to the next PLL. The loop parameters of this PLL and the previous one in the chain may be embedded in field-programmable gate arrays (FPGAs), and may take extra work with the FPGA vendor to get at the desired numbers.

The fifth PLL (PLL 5) is the RF head reference PLL. It is often designed with a very low loop bandwidth, such as 10 or 20 Hz. This loop is used to clean up noise on its reference so its output (50 MHz in this example) can be used as a very clean reference to the digital-to-analog-converter (DAC) clock PLL and to the transmit RF LO PLL. A very-low-noise VCXO is typically used in this PLL, and the loop response is such that it filters out most noise from the PLLs prior to it. The only reference noise that passes through this loop is in the approximate 1-to-10-Hz range.

The sixth PLL (PLL 6) is the transmit DAC clock. This PLL runs at the DAC sampling clock rate (400 MHz in this example) and has a loop bandwidth on the order of a few kilohertz. The noise from this loop is ideally 10 dB or more below that of the RF LO's noise, such that this loop is not a significant contributor to the system phase noise budget.

The seventh PLL (PLL 7) is the transmit RF LO. This PLL must be frequency agile (tunable to each channel) and is therefore often designed using a fractional-N PLL chip that can lower the in-band noise floor. Loop bandwidths are often in the 20-to-40-kHz range, and optimized for best noise. The PLL IC selected must have a very low noise floor in the 100-Hz-to-10-kHz range. The VCO in this PLL must have excellent far-out (1 MHz and greater offsets) noise.

The next step in the WiMAX AP transmitter frequency chain simulation is to put together a simulation that connects all the individual PLL simulations in series (Fig. 9). This simulation begins with the phase noise of the site controller TCXO (which is locked to a GPS reference) and ends with the transmit LO PLL. In between are PLL simulations of each PLL in the chain. Each PLL has at its input the output phase noise from the previous simulation block. The final output is the composite transmitter system phase noise (transmit DAC clock phase noise not included for simplicity), which is the red curve shown in Fig. 10.

Figure 10 also contains curves showing the output phase noise for each PLL in Fig. 9. By stepping through each result, and by understanding the loop response of each PLL, it is possible to draw conclusions about which PLLs in the chain contribute most significantly to the phase noise at the transmit LO for various offsets of interest. This also makes it possible to identify opportunities for improvement, and where phase-noise requirements can be relaxed. Equations can be written (one is shown) to integrate phase noise on any curve in the simulation output, for any integration bandwidth. Figure 10 shows that for this example system, the integrated transmit LO noise from 100 Hz to 5.5 MHz is -44.2 dBc (or 0.35 deg. rms), an excellent result for a PLL system with output at 2500 MHz.

Continue to page 3

Page Title

For this WiMAX AP example, the phase noise at different offset frequencies can be assessed as follows. The phase noise offset 1 to 10 Hz from the carrier affects transmitter phase wander (to some degree, frequency error) and baseband bus wander; this comes primarily from the 10 MHz TCXO (light green curve). No other PLL in the chain has a bandwidth low enough to filter phase noise in this region. If one did, it would need to have a very low phase noise contribution to make the filtering worthwhile. Improving phase noise in this region would probably require the use of a higher-performance TCXO or an OCXO in the site controller's reference loop.

The phase noise from 10 to 100 Hz can affect baseband wander, frequency error, and in certain systems, can even impact the relative phase error of smart antenna systems. Noise in this region (in the example system) comes primarily from the modem's 200-MHz reference clock. This could be improved by optimizing loop bandwidth for noise, or by using a higher-performance PLL/VCO. The noise in this region is also impacted by the 50-MHz PLL on the RF head. This could be improved by optimizing loop bandwidth for noise, or by using a higher-performance VCXO.

The phase noise from 100 Hz to 1 kHz comes primarily from the 50-MHz PLL on the RF head. This can pretty much only be improved by using a higher-performance 50-MHz VCXO. In this region, there may be a secondary contribution from the transmit LO PLL noise floor. This is the crossover region that just begins to impact the error-vector-magnitude (EVM) or relative-constellation-error (RCE) performance.

The phase noise from 1 to 10 kHz is mostly limited by the transmit LO PLL IC phase detector and charge pump noise. Improvements require the use of a higher-performance PLL IC. This region significantly impacts RCE/EVM performance. The phase noise from 10 to 100 kHz is a combination of transmit LO PLL noise floor and transmit LO VCO noise. This region impacts RCE/EVM performance and if it is poor enough, it can also degrade adjacent subcarrier modulation accuracy.

The phase noise from 100 kHz to 1 MHz can degrade close-in spectral mask, and can also impact EVM/RCE performance, although this far from the carrier, it is usually falling off rapidly enough to not be a significant issue. Improvements require loop optimization and/or a better VCO.

The phase noise from 1 MHz to 10 MHz impacts spectral mask. Poor phase noise performance in this region can limit the ability of a digital predistortion circuit to correct transmitter nonlinearities. This can be improved only by using a higher-performance VCO in the transmit LO PLL circuit. The phase noise from 10 MHz to 100 MHz contributes to the transmitter noise floor and can limit in-band spurious emissions. Improvements require the use of a higher-performance VCO in the transmit LO PLL.

While it takes a considerable amount of time to set up all the simulation blocks in Fig. 9, once everything is complete, it represents a powerful tool. For example, one can immediately see the effects on the system, of using a low cost VCO (poorer phase noise) at the modem's 200-MHz reference clock. This tool also answers questions that are otherwise difficult to answer, such as what effects will the transmitter system see, if the modem SerDes clock phase noise is allowed to degrade by 20 dB at offsets of 10 kHz and higher? The answer may well be that there is no system impact to the transmitter RF performance, since the 50-MHz PLL in the RF head is such an effective filter of that noise. However, that kind of degradation to the SerDes clock on the modem may violate digital timing and jitter requirements. Remember that every loop in the chain serves specific functions, and those functions have their own requirements. In addition, every loop in the chain has the potential to impact the loops farther down the chain, and this is what makes a simulation tool like this so valuable.

If simulations show that phase noise of any particular PLL must be improved to meet system performance requirements, a designer has several options. Some of these include

optimizing the PLL loop bandwidth for noise; choosing a better phase detector frequency (that lowers the PLL noise floor);

increasing the loop order (for better noise and spurious rejection; lowering the frequency control element phase noise (for example, using a better VCXO);

using higher-performance PLL ICs (to lower the charge pump noise); and

using a fractional-N approach and running at higher frequencies with external dividers.

In summary, with commercial modeling tools such as ADS from Agilent Technologies, it is possible to perform a simulation on the multiple loops of a transmitter in a modular fashion, so that the contributions of each can be examined as to their effects on final system phase noise. The example simulation presented here incorporated several subsimulations of PLL loop response and stability, as well as individual simulations for the phase noise of each PLL in a WiMAX AP frequency chain. These subsimulations were connected in series to form the AP frequency chain, and used to simulate transmitter system phase noise. This system of simulations gives designers insights into design improvements and optimizations, as well as opportunities for cost reductions and design reuse.

References

1. W. P, Robins, Phase Noise in Signal Sources, Peter Perigrinus, London, 1982.

2. Roland E. Best, Phase Locked Loops, McGraw-Hill, New York, 1997.

3. Ulrich L. Rohde, Microwave and Wireless Synthesizers, Wiley, New York, 1997.

4. Analog Devices, ADIsimPLL 3.0 design and evaluation software, available on the company's web site at www.analog.com.

5. National Instruments, WEBENCH PLL design tool available at www.national.com/analog.

6. Agilent Technologies, ADS design software suite, www.agilent.com.