Download this article as a .PDF

High-speed digitizers have enabled significant improvements in military electronic systems by converting analog input signals to the digital realm, where advanced digital-signal-processing (DSP) techniques can be applied. In a receiver, analog-to-digital converters (ADCs) are positioned at the output of an intermediate-frequency (IF) amplifier, and have enabled direct sampling of those signals at L-band frequencies from 1 to 2 GHz. These high-speed data converters show little compromise in AC performance compared to traditional IF sampling architectures.

But now, with the availability of such higher-speed converters as the ADC12DJ3200 family from Texas Instruments, direct conversion of RF input signals is possible at frequencies to 8 GHz and beyond. A 12-b ADC12DJ3200 digitizer can be used in single- or dual-channel modes, with single-channel sampling rates to 6.4 GSamples/s and dual-channel sampling rates to 3.2 GSamples/s. It represents the next step in the evolution of high-speed data converters and can benefit a wide range of applications, including communications, radar, electronic counter measures (ECM), electronic intelligence (ELINT), and signal intelligence (SIGINT) systems.

The ADC12DJ3200 ADC has a full-power 3-dB input bandwidth of 8 GHz but a usable frequency range of better than 10 GHz. For processing the faintest of signals, it features a full-scale (FS) noise floor of −151.8 dB/Hz in dual-channel mode, which drops even further to −154.6 dBFS/Hz in single-channel mode. The ADC incorporates a high-speed JESD204B output interface with as many as 16 serialized lanes which support data transfer rates as high as 12 Gb/s. The ADC (Fig. 1, shown on an evaluation board) has a full-power 3-dB input bandwidth of 8 GHz but a usable frequency range of better than 10 GHz. For processing the faintest of signals, it features a full-scale (FS) noise floor of −151.8 dB/Hz in dual-channel mode, which drops even further to −154.6 dBFS/Hz in single-channel mode.

The ADC incorporates a high-speed JESD204B output interface with as many as 16 serialized lanes which support data transfer rates as high as 12 Gb/s. The number of lanes can be configured in different ways for tradeoffs in bit rate. The converter includes synchronization capabilities (e.g., noiseless aperture delay and SYSREF windowing) to simplify system design with multiple elements, such as in phase-array and multiple-input, multiple-output (MIMO) antennas.

This next generation of data converters represented by the ADC12DJ3200 ADC—with a direct-sampling architecture that can be applied at S- or C-band frequencies—brings many attractive benefits to military electronic systems, including smaller system size, larger instantaneous bandwidth (IBW), and reduced signal-chain complexity. Of course, the capability to almost immediately process received signals from a radar or EW system in the digital realm will bring many additional benefits, once system designers apply advanced signal-processing techniques earlier in the system signal chain. Let’s take a closer look at these benefits.

Smaller Component Size

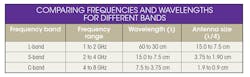

In military electronic systems, the use of higher frequencies involves signals with smaller wavelengths and smaller physical and electrical component sizes, thus affecting most components in the signal chain. These range from the antenna and filters to passive devices like matching elements or bypass capacitors. Radar systems rely on highly directed energy beams and can achieve precisely controlled beams through the use of beamforming techniques with a distributed, phased-array antenna. Such an antenna consists of many separate radiating elements, each with a phase shifter. Beams are formed by shifting the phase of the signal emitted from each radiating element so that the combined contributions of the antenna elements result in a high-power energy beam steered in a desired direction.

Since modern phased-array radars can have literally thousands of antenna elements to enable simultaneous tracking of multiple targets (Fig. 2), individual elements must be very small and operating at very low power levels. Thus, developing a radar system at S- or C-band frequencies with a much smaller electrical wavelength is a major motivation (see table). Operating at a higher frequency also comes with higher transmission path loss; however, techniques such as dual polarization exist to mitigate the increased signal attenuation. C-band weather radars, for example, can achieve ranges as great as 500 km and more.

Larger IBW

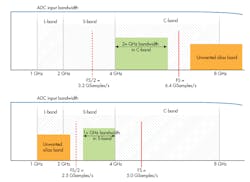

Perhaps the biggest motivation to moving to higher frequency bands is the larger available frequency spectrum, owing to the congestion of so many commercial and industrial applications at lower frequencies. S-band frequencies provide as much as 2 GHz IBW, while C-band frequencies offer as much as 4 GHz IBW—which is more than enough spectrum for frequency hopping, even for systems with larger bandwidth requirements. Direct RF sampling converters that provide frequency coverage to C-band naturally also enable frequency hopping across L-, S-, and C-band frequencies for even greater system design flexibility.

One of the key requirements for processing a higher IBW is sufficient converter sampling rate. Modern RF Gb/s sampling-rate data converters designed with advanced silicon complementary metal-oxide-semiconductor (CMOS) processes are capable of digitizing wide bandwidths with high power efficiency and minimal processing delays. High speed data converters, such as the members of the ADC12DJ3200 product family, support sampling rates to 6.4 GSamples/s for single-channel operation, along with an input bandwidth of greater than 8 GHz. This enables digitization of an IBW of better than 2 GHz at C-band frequencies (Fig. 3) and better than 1 GHz at S-band frequencies, while leaving adequate frequency range for the anti-aliasing filter transition band.

Numerous wideband defense electronic systems (such as ECM, ELINT, and SIGINT systems) are designed to operate over broad contiguous frequency ranges (e.g., DC to 18 GHz), although they traditional have covered that frequency range a bit at a time (such as in 1-GHz segments) due to the limitations of the digitizers. With a digitizer capable of wider IBWs, much faster spectrum scanning and response times are possible with those systems.

Reduced Complexity

As noted earlier, phased-array systems consist of thousands of separate elements which must each be small and thermally efficient to create an antenna array in a practical size with good long-term reliability. This is especially true when moving to the shorter wavelengths of S- or C-band frequencies. Direct RF sampling offers a very desirable architecture because it removes an entire frequency-downconversion stage within the receiver (Fig. 4). It is the elimination of a number of different high-frequency components, including a frequency mixer, amplifier, filter, and matching networks and power supplies for those components.

In addition to the savings in size, weight, and power (SWaP), elimination of those components also statistically removes potential sources of failure for improved overall system reliability. Maintaining the signal chain at a high frequency simplifies filtering requirements; the values of passive component elements required for filter construction such as resistors, capacitors, and inductors are much smaller, and those circuit elements are much smaller in size at the higher wavelengths.

Of course, direct RF sampling does present some differences to a system design compared to traditional superheterodyne receiver architectures where a frequency mixer translates a smaller portion of prefiltered frequency spectrum that will then be digitized by an ADC. In the direct RF sampling approach, the entire input bandwidth is digitized, including any unwanted signals and noise within that bandwidth. Thus, any receiver design with direct RF sampling requires effective RF filter analysis to ensure that undesired out-of-band interferers are sufficiently attenuated and don’t reduce the receiver sensitivity.

To minimize signal losses within the RF signal chain, impedance matching circuits are used to provide smooth impedance transitions from one component to the next. Therefore, when digitizing a large amount of frequency spectrum (as with an RF sampling converter), effective matching circuitry is essential. High-speed data converters such as the ADC12DJ3200 ADC with its well-behaved input return loss (S11) across the frequency range simplify the requirements for matching circuitry.

The ADC12DJ3200 family of ADCs provides the performance levels needed for direct conversion across a 3-dB bandwidth of 8 GHz and a usable bandwidth of 10 GHz. By adopting a direct RF sampling architecture, military (and other) receivers can now be designed with one or two fewer frequency-conversion stages, resulting in less components and a simpler receiver architecture. Benefits in system-level performance are yet to be seen, but will surely be realized by creative system-level designers.