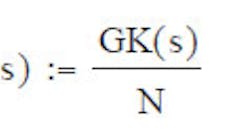

Phase noise in sampled phase-locked loops (PLLs) can impact the performance of a wide range of commercial and military systems, including communications networks based on phase modulation. As shown last month in the first installment of this three-part series, modeling approaches may differ depending upon whether a PLL is a continuous-time or sampled system, with nonlinear approaches needed for th latter. In this second article installment, it may be helpful to examine the results of a continuous PLL system so that it might be possible to see the differences when compared to a sampled system. The open-loop gain for a continuous system is

Figure 3 shows a plot of open-loop gain (magnitude versus frequency) for a continuous system with an open loop bandwidth set to about 3 kHz, while Fig. 4 shows a plot of openloop phase for a continuous system. The closed-loop transfer function is given by:

When this function is plotted, it provides the familiar response shown in Fig. 5, a plot of closed-loop magnitude as a function of frequency. Figure 6 shows the familiar closedloop phase response as a function of frequency.

The open-loop gain for a sampled system is given by Eq. 38. In this case, the gain has been scaled by a factor of T to keep the value correct. Also, n has been reduced from infinity to 5 to speed the calculations. The results of Eq. 38 are plotted in Fig. 7 on a linear scale for open-loop magnitude as a function of frequency. The open-loop gain is aliased about each harmonic of the sampled frequency. The same information is plotted in Fig. 8 on the more familiar log scale so that the gain and phase margin can be more easily seen in this plot of open-loop magnitude response. Figure 9 shows the measured open-loop gain of the test PLL, while Fig. 10 shows the open-loop phase with sampling in a plot of open-loop phase as a function of frequency.

Compared to the continuous time system, the open-loop gain in the sampled system passes through unity gain at a higher frequency and that the phase margin is reduced at this frequency.

The corresponding closed loop transfer response with sampling, Tr'(s), is given by Eq. 39. This is not a true transfer response as it is the output phase divided by the sampled input phase. Figure 11 shows a plot of the closed-loop transfer response with sampling (closed-loop magnitude versus frequency) while Fig. 12 shows the closed-loop response of the test PLL. Figure 13 provides a plot of the closed-loop phase with sampling.

To continue the analysis, at this point the functions are redefined as a function of sampling frequency so that the effect of different sampling frequencies may be observed later.

The next part of this analysis will examine the effect of sampling on the phase noise of the PLL synthesizer. The main sources of noise are free-running VCO noise, phase detector noise, thermal noise in the loop filter components, and reference oscillator noise. (Divider noise is included with the phase detector noise.) In analyzing the phase noise of the VCO (Fig. 14), the different segments (in distance from the carrier) should first be defined. Let the SSB phase noise in the far-off region, where it has an f0 profile, be called by the term L0 , with the offset f0. Similarly, in the region where the phase noise has an f-2 profile, let the phase noise be called by the term L2 and the offset f2. Finally, in the region where it has an f-3 profile, let the phase noise be known as L3 and the offset f3.

Then, for a typical oscillator such as the one measured above, the noise (in dBc/Hz) and offset frequency (in Hz) parameters are L0 = -155, f0 = 3 x 106, L2 = -126, f2 = 100 x 103, L3 = -70, and f3 = 1 x 103. The f -3 section of the noise due to 1/f noise in the oscillator circuit is modeled by Eq. 42:

The f -2 section due to peaking of white noise by oscillator is modeled by Eq. 43:

and the broadband white noise due to thermal noise and the noise figure of the active device is modeled by applying Eq. 44.

Combining these noise contributions results in an overall noise model of the oscillator, Loscn(s), as described by Eq. 45.

Figure 15 shows a plot of modeled noise for the free-running VCO. The phase noise at the output of the loop is made up of the noise when n = 0 and the sum of the output-noise, divided by N, which appears as an error signal at the phase detector and is acted on by the equivalent transfer function.

The phase noise due to the loop's action on the n = 0 component of oscillator noise can be described by the parameter Losc1(s) as defined in Eq. 46:

In addition, the phase noise due to the loop's action on the n 0 component of oscillator noise can be described by the parameter Losc2(s, fs) as defined in Eq. 47.

The noise of oscillator after sampling L'osc1 is given by Eq. 48.

The overall noise due to the oscillator in the loop, Losc(s, fs), is the sum of the two components of oscillator noise as shown in Eq. 49.

These various components of phase noise for the oscillator are plotted in Fig. 16, where

Losc is the total contribution to the overall noise after the action of the loop; Loscn is the noise of the free running oscillator; Losc1 is the noise due to the n = 0 component; and Losc2 is the noise due to n ? 0 components.

Continue to page 2

Page Title

Thermal noise, due to the real part of the impedance of the loop filter, modulates the VCO to give phase noise at the output of the VCO. In performing thermal noise calculations, the absolute temperature, T, is 290 K while Boltzmann's constant, k, is 1.38 x 10-23 mKs. From FM theory, the SSB noise due to modulation by thermal noise is given by Eq. 50:

Z(s) = the impedance of the loop filter

Equation 50 can be simplified to Eq. 51:

This noise combines with the VCO phase noise before being modified by the loop, yielding Eq. 52:

The combination of the modulation and phase noise is depicted in Fig. 17, while the sampled version of the combined VCO noise and modulation noise is depicted in Eq. 53.

The phase noise due to the loop's action on the n = 0 component of oscillator noise can be found from Eq. 54

The phase noise due to the loop's action on the n ? 0 component of oscillator noise can be found from Eq. 55,

where L'osceff1(s,fs) is given by Eq. 56:

The overall noise, Losctot (s,fs), due to the oscillator and the noise due to modulation of the oscillator by thermal noise in the loop filter components is the sum of the absolute value of the two components of oscillator noise as shown by Eq. 57:

In performing an analysis on the phase-detector noise, the term "phasedetector noise" is used to include noise due to the charge pumps, the reference dividers, and the programmable dividers since it is not possible to isolate the cause of noise within the individual components or function blocks in many single-chip PLLs. For any given sampling frequency, the effect that the phase-detector components have on the loop is essentially the same irrespective of the cause or source of the noise.

The phase-detector noise for any given chip at a particular comparison frequency is usually determined by means of measurements with a spectrum analyzer or phase-noise test set. Typically, for the model LMX1511 chip from National Semiconductor used in the test PLL, the value is equivalent to approximately -163 dBc/ Hz at a comparison frequency of 25 kHz. Often, the measure termed "figure of merit" (FOM) is used by component manufacturers where the noise is referenced to a 1-Hz bandwidth. From this FOM, the noise can be extrapolated for any sampling frequency. This relationship usually holds over a wide range of frequencies but may eventually break down at higher frequencies.

Next month, the final installment in this three-part article series will point out some differences in the effects of phase noise in continuoustime and sampled PLL sources, using computer simulations and measured data for comparisons. The noise due to the reference oscillator in a PLL frequency synthesizer will be analyzed, and then combined with other noise sources in an overall evalution of the effects of sampling on a test PLL circuit. By using simulations, it is possible to understand the influence of specific noise sources, such as the phase detector noise, on the overall noise performance of a PLL system, and how those different contributions compare in a contant-time PLL versus a sampled PLL system. In addition, next month's final installment of this article series will detail the merits of using free PLL simulation programs, with linear modeling capabilities, to approximate the performance of timesampled, nonlinear PLL frequency synthesizer systems.