What Techniques Boost PA Efficiency?

This file type includes high resolution graphics and schematics when applicable.

As more companies and industries embrace gallium-nitride (GaN) technology for use in wide-bandwidth and high-power applications, the need for power-efficient and compact typologies is increasing. Booming areas for RF/microwave applications include portable electronics, electronic warfare (EW)/military, and wireless infrastructure. For all of these applications, the efficiency of a power amplifier’s (PA’s) operation is critical. GaN’s performance capability has required some significant ingenuity on the part of design engineers to take this technology to the next level of efficiency and deployability.

GaN technology is very flexible and robust, which has led to significant discussions on how a designer can cleverly manipulate the greatest efficiency and power dissipation from this highly promising semiconductor. “For example, GaN devices/amplifiers are routinely operating at 50 V with efforts pushing this to 65 V,” notes Timothy Boles, technology fellow and director of strategy for MACOM. “Since power equals current multiplied by voltage for a fixed output power, doubling the supply voltage will mean that the amplifier can be designed with a device the only requires half to one-fifth of the current compared to other active-device material systems.”

A few major factors relate to the efficiency of a power amplifier: typology, impedance matching, thermal management, input bias, and bandwidth. Also, several parameters require a tradeoff when considering increasing the efficiency—namely linearity, modulation accuracy, gain, spectral regrowth, size, and cost. It helps to know the dynamics of these design considerations as well as the tradeoffs to drive the best performance from a PA. With many military organizations switching to commercial-off-the-shelf (COTS) components, these concerns also impact the military organizations looking to increase their tactical networking capability to better compete on the modern battlefield.

Many new techniques, such as envelope tracking (ET) and digital pre-distortion (DPD), enhance PA efficiency. But hardware-level efficiency will still limit the maximum efficiency of the device. For this reason, designers have sought PA circuit designs that could enable greater efficiency while being dependent upon the instantaneous power requirement of the transmitted signal. A typology that has experienced increased adoption is the Asymmetric Doherty PA or Doherty PA.

The Doherty typology is used to induce a loading effect on the output of a PA—generally a Class-B main amplifier and Class-C peaking amplifier. That load is then adjusted to an optimized efficiency curve based upon the RF signal level. According to Mark Faulkner, vice president, RF Integrated Solutions Engineering for Microsemi, “Though a bit tricky to design, lower-frequency narrowband microwave amplifiers in a Doherty configuration with a peaking amplifier and a carrier amplifier demonstrate great efficiency. The Doherty is highly nonlinear and may require additional digital signal processing (DSP) for the linear modulation schemes used in communication architectures.”

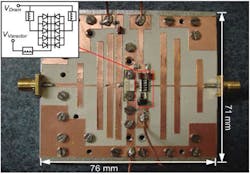

The dynamic loading effect of a Doherty PA is induced by a secondary amplifier, known as the peaking amplifier. This amplifier generates an additional virtual load at the output of the main amplifier. The behavior of the peaking amplifier is controlled by the instantaneous power requirement of the amplifier system. Often, the input signal is delivered through a 90-deg. hybrid coupler for power splitting to each amplifier.

The peaking amplifier is connected to the power splitter with a quarter-wave transmission line. It has an unobstructed connection to the output load. The main amplifier, in contrast, is directly connected to the power splitter and linked to the output load through a quarter-wave transmission line. This configuration ensures that the signals from each amplifier will be delivered in-phase to the load. Ideally, only the main amplifier will operate for low-power signal conditions.

Under large-power signal conditions, the peaking amplifier will turn on and increase the effective load at the output. The increased parallel loading at the output of the main amplifier reduces the effective load as seen by the main amplifier. As a result, the main amplifier can produce greater current and power. This approach limits the increase in voltage output for the main amplifier. It also limits clipping or increased distortion at higher voltage levels.

Matching is required at the input of both the main and peaking amplifiers. The output matching should be designed using sophisticated load-pull techniques or highly refined models. For Doherty design cases, in which the peak amplifier is larger than the main amplifier, additional signal power should be delivered to the peak amplifier. This approach improves efficiency. Commercially available modules, which drive Doherty PAs, enable control of the amplitude and phase of each amplifier in the configuration.

The Asymmetric Doherty configuration can generally achieve an increased average efficiency of greater than 50%. In contrast, an ideal Class-B amplifier—with an average efficiency of 27% and a symmetric Doherty configuration— often exhibits 5% less efficiency than an Asymmetric Doherty.

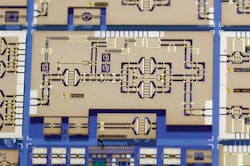

This file type includes high resolution graphics and schematics when applicable.

Other Typologies

This file type includes high resolution graphics and schematics when applicable.

Beyond Asymmetric Doherty typologies, there are other multi-amplifier typologies that can increase efficiency beyond the capability of a single-amplifier architecture. “Another high-efficiency topology, given enough drain-voltage headroom, is the shared current topology,” states Faulkner. “The efficiency of a balanced amplifier stage can be doubled by sharing the current between the upper and lower devices. Using this stack topology, half of the drain voltage is dropped across the top device with a DC-elevated source and gate voltage. Care must be taken to choke the RF in the shared bias between the upper and lower devices, as they are out of phase when quadrature-balanced.”

Input and output impedance matching is another critical stage in the design of a PA, as the bandwidth, frequency, and load impedances all dictate the specification requirements for the matching circuitry. GaN devices benefit from greater efficiency in these stages, which is partially due to the decreased current through the matching circuitry. This, in turn, reduces current and resistive losses through the conductors of the matching elements.

The lower current also reduces high-frequency losses in the combining/transformation networks. However, adapting matching circuitry for GaN devices does become more complicated as a function of the effects of increased voltage swing, bandwidth, temperature, and low impedance on the output of a GaN PA.

Load-pull and source-pull techniques are a common method for evaluating the impedance performance parameters of a PA design. They also enable an effective description of what impedance matching specifications may be required in real-world conditions. Load/source-pull techniques consist of varying the impedance at the load or source of a device while it is operating under predicted operational parameters.

“Microsemi uses load pull in order to determine the optimum power, gain, efficiency, or linearity impedance of a device,” notes Faulkner. “This information is combined with Smith Charts and linear simulation to synthesize the matching networks. We also use nonlinear simulation tools for matching synthesis, depending on the accuracy and robustness of the nonlinear device model.”

The behavior of transistors and fundamental circuit elements changes with temperature, packaging, and the materials used. As a result, the fabrication of a device come into play significantly. Boles shares, “Thermal management and thermal modeling are the keys to producing high-reliability/high-efficiency power amplifiers. Virtually all device characteristics—breakdown voltages, leakage currents, transconductance, gain, PAE, etc.—degrade with increasing temperatures.” Careful design and modeling of the thermal characteristics of a package and its material components is becoming more relevant. As PAs shrink in size and power efficiency, thermal performance is becoming a more critical feature.

Many common material solutions enable more thermally conductive packages. “Both materials and packaging are key to a reliable and efficient design,” says Faulkner. “The thermal design goal is to create a low-thermal-resistance path from the GaN-transistor junction to the system heatsink, which might be metal fins in a convective airflow. Typically, these low-thermal-resistance materials are further constrained to also match the expansion coefficient of GaN. Depending on the device size and bonding material, copper (Cu), copper tungsten (CuW), and copper-molybdenum (CuMo) are often used in this low-thermal-resistance path.”

Although thermal characteristics largely contribute to a package’s thermal behavior, several design techniques can lead to more thermally efficient assemblies. Faulkner continues, “This path must also be uninterrupted, meaning channels and voids to route DC cannot be located under the devices. Assembly processes and equipment must ensure that voiding in the attach material, which bonds the GaN to the package, is minimized. Also, the mating of metal-to-metal interfaces needs to be specified to tighter flatness specifications to improve heat flow.”

As the performance of GaN and other high-powered, high-frequency, and compact devices continues to advance, designers will increasingly be forced to delve into the minute details of a device’s design. Circuit techniques, matching, thermal management, materials, and packaging are just one aspect of a greater landscape of challenges. Fortunately, software and computerized tools also are increasing in capability. Soon, design engineers may find that they are relying more on these tools to complete the design of the latest devices.

This file type includes high resolution graphics and schematics when applicable.

About the Author

Jean-Jacques DeLisle

Jean-Jacques graduated from the Rochester Institute of Technology, where he completed his Master of Science in Electrical Engineering. In his studies, Jean-Jacques focused on Control Systems Design, Mixed-Signal IC Design, and RF Design. His research focus was in smart-sensor platform design for RF connector applications for the telecommunications industry. During his research, Jean-Jacques developed a passion for the field of RF/microwaves and expanded his knowledge by doing R&D for the telecommunications industry.