Developing Designs For RFID Transponder Using DTMOS

Transponder design for radio-frequency-identification (RFID) circuits must overcome many of the challenges faced by other low-power electronic applications. RFID transponder circuitry must be low in cost, and must operate over long periods of time on limited power sources. Earlier in the article series (Microwaves & RF, September 2006, p. 57 and October 2006, p. 82), basic design strategies were presented for designing RFID transponder integrated circuits (ICs) and how they could be applied in different circuits. In this final installment of this article series, some advanced RFID transponder design strategies will be explored, with chief goals of saving power and saving money.

The cost of a transponder design depends on several factors and not just the cost of the silicon alone. In fact, the costs of the chip-fabrication process (in terms of its complexity and maturity and the resulting yield) can generally be controlled by the circuit designer. As a rule of thumb, the economies of RFID for a supply-chain application begin to fall short when the die area exceeds 1 square millimeter.

An RFID transponder's power-supply requirements can present a difficult-to-predict challenge for a designer since an RFID tag's power varies over roughly three decades when moving from the minimum to the maximum range of the system. Although the typical power available for UHF RFID tags is on order of a hundred microwatts, the problem is not limited to power dropouts alone. Even at short distances, it is possible to put sufficient power into the tag to induce electrical overstress. Tags also have to work over a nominal temperature range from –25 to +40°C and an extended temperature range from –40 to +65°C based on the EPC Gen2 standard.

The cost and power requirements greatly impact the choice of technology used to fabricate an RFID transponder IC. As noted in the earlier parts of this article series, Schottky contacts provide low turn-on voltage, low junction capacitance, and high current drivability in RFID transponder designs. Alternatively, there have been efforts to employ newer technologies such as BiCMOS and silicon-on-sapphire (SOS), which offer excellent low power performance. But there are downsides to each approach. Schottky contacts are not routine in CMOS processes, and usually require post-processing steps. The other technologies, BiCMOS and SOS, are too expensive for most RFID transponder applications.

Another option for implementing low-power circuit requirements is dynamic-threshold-voltage MOSFET (DTMOS) technology. It can be fabricated inexpensively using bulk silicon CMOS technology. Both advantages are well suited for the development of the next-generation UHF RFID transponder, which is described in this article. This article will first introduce the fundamentals of DTMOS. Then, the DTMOS implementations in the digital, analog and RF domains will be highlighted as UHF RFID transponder contains circuitries covering all three domains. Finally, the chip implementation of DTMOS-Band-Gap reference circuit of UHF RFID transponder, following EPC Gen2 specifications will be demonstrated.

DTMOS is basically a MOS transistor with an interconnected well and gate (Fig. 1). For twin-well p-substrate CMOS processes, only P-type DTMOS can be used due to the fact that only their N-wells can be controlled and fabricated independently, since the P-well of N-type DTMOS has a common and low-ohmic path to the P-substrate. However, N-type DTMOS is available in processes with deep N-well feature. DTMOS operates like weak-inversion MOS operation, with similarities to bipolar operation in a lateral PNP. The drain current of a weak-inverted MOS transistor and the collector current of a lateral PNP (both in saturation) are given by:

where:

F = FBJT = VBE

for a bipolar transistor and

F = FWIM = GS– VT).COX/(COX + Cdepletion)>

for a weak-inversion MOS transistor.

The value of the depletion capacitance depends on the width of the depletion layer, which in turn depends on the well doping characteristics and the voltage drop in the silicon near the source junction. Hence, the factor depends on the applied well-source voltage and on the applied well-source voltage via the threshold modulation effect.

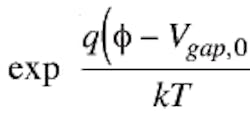

DTMOS can be viewed as a lateral bipolar PNP with an extra gate over the base. Based on this view, DTMOS’s drain current is primarily determined by the voltage across the source-well junction, which results in an ideal exponential (bipolar-like) relation between VGS and ID. Due to the presence of the interconnected gate-well, there is a built-in voltage FGW between the gate and well. Voltage FGW is subdivided over the gate oxide and over the silicon due to capacitive division. Denoting the voltage drop in the silicon due to FGW as the barrier lowering voltage Fb1, it can be shown that the drain current of a DTMOS is:

The barrier lowering voltage Fb1 is given by:

which is a function of FGW and of a number of process parameters. Derivations from refs. 1-4 show that:

The key results from these derivations are as follows:

• The apparent bandgap of a DTMOS device is 0.6 V compared to 1.2 V for a silicon PN junction.

• The DTMOS device follows an ideal exponential characteristic D a exp(qVGS/kT)>

• The DTMOS device’s lateral current is a factor of exp(qFb1/kT), which is larger than ordinary lateral PNP counterpart.

• The apparent bandgap voltage is temperature dependent.

Page Title

An initial, successful design fabricated with quarter-micron DTMOS technology operated at 77 K using a supply voltage of 0.6 V with the body substrate tied to the fixed forward bias.5 Later experiments involved gate controlled lateral bipolar transistor (GCLPNP)6 and silicon-on-insulator (SOI) MOSFET7 technology with the substrate tied to the gate terminal. The first technology is used for a miniature lowpower analog application while the second is typically the best candidate for ultralow-power CMOS.

DTMOS technology shows an impressive figure of merit in its gate-delay/power-consumption product compared to conventional CMOS. DTMOS also shows superior performance in RF circuits. In conventional CMOS, technology scaling to smaller feature sizes and threshold voltages (VTH) increases the operating speed. However, lowering VTH also leads to degraded subthreshold MOSFET behavior. The standby current increases in static circuits, thus limiting VTH to 0.4 V. DTMOS can possibly overcome such constraints, especially operation at very low VDD and low VTH with steep subthreshold characteristics. With DTMOS, the gate input voltage forward biases the substrate, hence VTH will decrease according to the well-known body effect equation8:

Based on this equation, DTMOS can achieve low VTH in its "on" state. At the same time, in its "off" state, it maintains a steep subthreshold slope similar to that of non-scaled conventional MOSFETs to minimize reverse leakage current. This is accomplished by varying the VBS component in the body effect equation in the DTMOS "on" and "off" states.

Several groups have demonstrated various physical implementations of bulk-DTMOS (B-DTMOS) for digital circuits. In early work, two groups created B-DTMOS logic circuitry by tying the CMOS gate and well together.9,10

This approach has the advantage of efficient use of substrate real estate. Still, results from both research groups exhibited limited VDD, in the range of 0.6 to 0.8 V. Seizo Kakimoto and his research team made some improvement on this VDD limitation.11 Their work involved the use of a self-adaptive power-supply scheme (Fig. 2) to generate the necessary voltage supply, so that their BDTMOS achieved enhanced stability compared to earlier work, at the expense of additional control circuitry and larger chip size.

Another approach was revealed at the 1996 IEDM: an ultra-low-power logic circuit using modified advanced isolation (SITOS) CMOS with gate-to-shallow-well contacts (SSS-C) to achieve BDTMOS. By using a modified CMOS process, the parasitic well capacitance was minimized and a higher operating frequency was achieved.12

Besides using B-DTMOS in a simple static CMOS logic configuration, other logic schemes based on DTMOS were proposed by Elgharbawy in the form of domino B-DTMOS (B-DTPMOS) logic, which route the clock signal to the substrate.13 Connecting the system clock in dynamic circuits to the common substrate of all the NMOS transistors improves the switching speed and the driving capability of the domino-like circuits at the cost of a slight increase in power consumption compared to conventional subthreshold domino schemes. Furthermore, B-DTPMOS can be combined with the B-DTNMOS for even faster operation and higher driving capability with a slight increase in power consumption. Still, it yields a 43.2-percent energy savings compared to the conventional subthreshold domino scheme. These results indicate that the proposed RFID transponder scheme is well suited for battery-powered devices, where energy conservation is a primary concern.

Most of the early work on DTMOS has focused on digital circuitry, due to the low power capability of the technology. But recently, two groups demonstrated promise for DTMOS in analog applications. One group achieved a low-voltage (1-V) operational amplifier (opamp) with 35.7-MHz unity-gain frequency and 64-deg. phase margin under load conditions of 5 pF and 10 kΩ.14

The other group fabricated a stable bandgap reference circuit using dynamic-threshold MOS transistors.15 Suitable for low-voltage, low-power ICs which can tolerate moderate accuracy, the bandgap-reference circuit runs on supply voltages as low a 0.85 V and generates reference voltage of 0.65 V while consuming only 1 µW power. The die occupies only 0.063 mm2 area using a standard 0.35-µm CMOS process.

Apart from digital and analog applications, researchers from Taiwan National Chiao-Tung University pointed out the potential of DTMOS in RF applications as well.16 They implemented and studied a high-speed DTMOS structure using a standard 0.18µm CMOS process with deep N-well isolation from TSMC (Fig. 3). The DTMOS structure was found to exhibit a resistive nature at its input port because of the tied body gate; the forward bias VBS was found to enhance the current gain and hence improve the frequency response.

In one experiment, the group reported that under low drain current, DTMOS exhibits enhanced cutoff frequency (ft) and maximum frequency oscillator (fmax) performance. For example, they observed ft of 65 GHz and fmax of 52 GHz for a drain current of 12.5 mA. The source-body capacitance extends the bandwidth but flattens the power gain. The input third-order-intercept-point (IIIP3) performance is also better for DTMOS than for conventional CMOS by 3.3 dB. The better linearity at low drain current suggests that DTMOS is an attractive process for RF amplifiers, although the output power is lower than conventional CMOS because of substrate losses due to the source-body capacitance.

DTMOS is a strong candidate for driver circuitry compared to CMOS, with its better transconductance-to-drain-source-current (gm-to-IDS) ratio at low current levels, indicating low channel resistance for DTMOS. Due to contribution of the parallel parasitic bipolar transistor, DTMOS exhibits excellent potential for driver circuitry. A positive feature of DTMOS is that its inherent body-to-source diode serves as electrostatic-discharge (ESD) protection, eliminating the need for additional ESD circuitry.

Page Title

Based on the results presented above, the current authors feel that DTMOS is an excellent candidate for a UHF RFID transponder rectifying device, as an alternative to Schottky contacts. The lowpower performance of DTMOS will also help to cut the power consumption of the RFID digital block.

The authors' group at Multimedia University, in collaboration with Silterra (Malaysia), has been involved in the development of a DTMOS UHF RFID transponder IC. One of the first projects involved the successful design, fabrication, and test of a bandgap-reference (BGR) circuit, employing the Silterra fabrication technology. A stable voltage reference is a vital component as part of the on-chip supply for an RFID transponder IC. It generates the drain voltage (VDD) and is part of the stable power rail for the transponder's digital circuits and an on-chip oscillator. A well-designed reference source must remain stable with process variations, voltage, and temperature, without making adjustments in the fabrication process.

Conventional BGRs using CMOS technology typically employ diode-connected parasitic substrate vertical PNP transistors or lateral PNP transistors as diode elements. Typical bandgap designs require at least several tens of microwatts of power and provide a default output voltage of around 1.25 V, which is nearly the same as the bandgap voltage of silicon, extrapolated to 0 K .17

The VDD supply voltage achievable in a UHF RFID IC is at the range of 1 to 1.5 V only for optimum range devices.18 A goal for a regulated VDD RFID digital core supply is less than 1 V. Therefore, a conventional BGR is not suitable for RFID applications for two reasons: its high power consumption and relatively high reference voltage, and the minimum supply voltage (VDD) required for the BGR. The solution proposed by the authors is shown in Fig. 4, a DTMOS BGR.

For the back-end of the device design, common layout techniques such as common centroid layout and dummy transistor techniques were employed to ensure device matching. High-resistance polysilicon resistors were used since they provide the best resistivity (Ω/square) among the resistor options available in the process, with a goal of minimizing the chip area. Simulation results were based on Silterra foundry HSPICE models. Due to the nature of DTMOS, there is the potential of the drain bulk junction being forward biased. Usually, SPICE (HSPICE) models fail to accurately predict device behavior for this scenario.

Figure 5 shows a micrograph of the DTMOS BGR. All measurements were performed on a wafer-probe station using an HP4156B parameter analyzer from Agilent Technologies (www.agilent.com). The measurements were generally in agreement with the simulations, as the table reveals.

The main contribution of B-DTMOS will be for the fabrication of a series of standard digital cells for the digital modules of UHF RFID transponders. B-DTMOS offers excellent digital performance under ultra-low-voltage conditions. Its lower leakage currents and higher speed compared to conventional CMOS circuitry imply great promise for future designs, although it is expected that the new digital cells will consumer larger chip areas than CMOS due to the additional complexity of the control circuitry.

In addition, DTMOS shows great promise for RF applications. Several researchers have explored the potential of the process for rectification, as an alternative to Schottky contacts. This would support low-cost production in a standard CMOS process compared to the post-processing efforts needed to fabricate Schottky contacts. Work continues with Silterra (Malaysia) to design a UHF RFID transponder IC using DTMOS on a standard, low-cost 0.18µm CMOS process, at present using a DTMOS structure in the design of the modulator and demodulator.

ACKNOWLEDGEMENT

This work was supported by Silterra Malaysia under its Malaysia University Multi Project Wafer (MPW) program. We also wish to thank Emerald Systems Sdn. Bhd. for providing the support to use the Mentor Graphics Tools.

REFERENCES

- H. Banba, H. Shiga, T. Miyaba, T. Tanzawa, S. Atsumi, and K. Sakui, "A CMOS Bandgap Reference Circuit with Sub-1-V Operation," IEEE Journal of Solid State Circuits, May 1999, Vol 34-5, pp. 670-674.

- D.B.M. Klaassen, J.W. Slotboom, and H.C. de Graaff, "Unified apparent bandgap narrowing in n- and p-type silicon," Solid State Electronics, February 1992, Vol. 35, p. 25.

- S.M. Sze, Semiconductor Devices, Wiley, New York, 1985.

- R.F. Pierret, Field Effect Devices, Addison-Wesley, Cambridge, MA, 1990.

- G. Baccarani, M.R. Wordeman, and R.H. Dennard, "Generalized scaling theory and its application to a 1/4 micrometer MOSFET design," IEEE Transactions on Electron Devices, April 1984, Volume 31, No. 4, pp. 452–462.

- Z. Yan, M.J. Deen, and D.S. Malhi, "Gate controlled Lateral PNP BJT: Characteristics, Modeling and Circuit Applications," IEEE Transactions on Electron Devices, January 1997, Vol. 44, No. 1, pp.118-128.

- F. Assaderaghi, D. Sinitsky, S.A. Parke, J. Bokor, P.K. Ko, and C. Hu, "Dynamic Threshold Voltage MOSFET (DTMOS) for Ultra-low Voltage VLSI," IEEE Transactions on Electron Devices, March 1997, Vol. 44, No. 3, pp. 414-422.

- P.R. Gray and R.G. Meyer, Analysis and Design of Analog Integrated Circuits, 3rd ed., Wiley, New York, 1993.

- Yu-Cherng Hung and Bin-Da Liu, "0.75-V subthreshold CMOS logic using dynamic substrate bias," Proceedings of the 2004 IEEE Asia-Pacific Conference on Circuits and Systems, December 6-9, 2004, Vol. 1, pp. 345–348.

- L.S.Y Wong and G.A. Rigby, "A 1 V CMOS digital circuits with double-gate-driven MOSFET," IEEE International Solid-State Circuits Conference, February 6-8, 1997, pp. 292–293.

- S. Kakimoto, T. Okuno, Y. Iwase, Y. Yaoi, F. Yoshioka, K. Kimoto, M. Nakano, K. Kawashima, S. Morishita, K. Sugimoto, T. Shiomi, T. Okumime, K. Kataoka, A. Shibata, S. Toyoyama, Y. Satoh, K. Fujimoto, K. Tatsumi, H. Kotaki, and A. Kito, "Self-corrective device and architecture to ensure LSI operation at 0.5 V using bulk dynamic threshold MOSFET with a self-adaptive power supply," IEEE International Solid-State Circuits Conference, pp. 402–502.

- H. Kotaki, S. Kakimoto, M. Nakano, T. Matsuoka, K. Adachi, K. Sugimoto, T. Fukushima, and Y. Sato, "Novel bulk dynamic threshold voltage MOSFET (B-DTMOS) with advanced isolation (SITOS) and gate to shallow-well contact (SSS-C) processes for ultra low power dual gate CMOS," International Electron Devices Meeting, December 8-11, 1996, pp. 459–462.

- W. Elgharbawy and M. Bayoumi, "New bulk dynamic threshold NMOS schemes for low-energy subthreshold domino-like circuits," IEEE Computer Society Annual Symposium on VLSI, February 19-20, 2004, pp. 115–120.

- H.F. Achigui, C.J.B. Fayomi, and M. Sawan, "A DTMOSbased 1 V Opamp," 10th IEEE International Conference on Electronics, Circuits, and Systems, December 14-17, 2003, Vol. 1, pp. 252–255.

- A. J. Annema, "Low-power bandgap references featuring DTMOS," IEEE Journal of Solid-State Circuits, July 1999, Vol. 34, No. 7, pp. 949–955.

- Chun-Yen Chang et al., "Investigations of bulk dynamic threshold-voltage MOSFET with 65 GHz "normalmode" ft and 220 GHz "over-drive mode" ft for RF applications," Symposium on VLSI Technology, June 12-14, 2001, pp. 89–90.

- K.E. Kuijik, "A precision reference voltage source," IEEE Journal of Solid State Circuits, June 1973, Vol. SC-8, pp. 222-226.

- J.P. Curty et al., "Remotely powered addressable UHF RFID integrated system," IEEE Journal of Solid-State Circuits, November 2005, Vol. 40, No. 11, pp. 2193–2202.