60-GHz PLL-Based Modulator Boosts Radar Applications

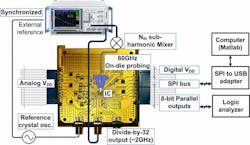

Significant research efforts have been made to realize a cost-effective CMOS IC radar for automotive, security, and presence-detection applications. At 60 GHz, sufficient bandwidth is available to achieve the range resolutions needed for high-resolution velocity detection. To realize this capability, Wanghua Wu, Robert Bogdan Staszewski, and John R. Long from Marvell Semiconductor Inc. have designed and implemented a 60-GHz frequency-modulated, continuous-wave (FMCW), digitally intensive transmit modulator. This modulator is based upon a multi-rate, all-digital phase-locked-loop (PLL) architecture.

To improve the system’s chirp linearity, a high-rate digitally controlled oscillator (DCO) clock is used. This DCO is realized from switched-metal capacitors, which are distributed across a transformer-coupled resonator for a 10% tuning range with roughly 1-MHz resolution at 60 GHz. This feature allows the modulated paths to have clock-cycle precision in time.

The measured root-mean-square (RMS) frequency error of the FMCW signal reaches 117 kHz for a 62-GHz carrier. The modulator covers 1.22 GHz with RMS jitter response of 590.2 fs. Settling time was measured down to 3 {micro}s with reference spur levels of -74 dBc and no other significant spurs. See “A 56.4-to-63.4 GHz Multi-Rate All-Digital Fractional-N PLL for FMCW Radar Applications in 65 nm CMOS,” IEEE Journal Of Solid-State Circuits, May 2014, p. 1081.