Shrinking cell phones have required shrinking components, including the power amplifier (PA). In just the last four years, the PA module in GSM cellular handsets has shrunk from 10 × 10 mm to a mere 5 × 5 mm (a model TQM7M4006 from TriQuint Semiconductor, for example). But in spite of the size reduction, performance must also improve, requiring clever design strategies. For example, to maintain high power-added efficiency (PAE) losses in the PA's output matching network should be minimized. The following approach shows how the use of an overlay inductor for that matching network can enhance GSM PA module performance even with the continuing reduction in size.

Most GSM PAMs use microstrip transmission lines or surface-mount inductors for the required inductance in the output match. This must be high-quality-factor (high-Q) inductance for good RF performance, requiring relatively wide microstrip lines. For example, the TQM7M4014 PA has a matching inductor realized by microstrip with width of 400 µm and length of 6650 µm. Due to size constraints, the use of microstrip with these dimensions is not practical for the design of a 5 × 5-mm GSM PAM. Reducing the size of the microstrip would increase the associated loss and compromise performance, so a different approach, such as an overlay inductor was required. Such was the approach used in the development of the 5 × 5-mm TQM7M4006 GSM PAM.

Transmission lines in the form of microstrip, stripline, or coplanar wave-guide are often used as layout structures to create inductance in the design of monolithic microwave integrated circuits (MMICs), RF integrated circuits (RF ICs), and RF modules. such transmission lines are usually positioned on top metal or on buried metal, inside the substrate with a ground-plane layer down below. The benefits of using transmission lines as inductors include lower loss compared to chip inductors, smaller size than coil inductors, and the ability to be made into almost any shape to save space.

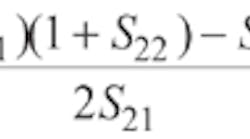

To estimate how much serial inductance is in a transmission line, a simple one-port S-parameter measurement with the other port terminated to ground can be used to calculate the impedance; the inductance is then derived from the imaginary part. This calculation works well below 1 GHz for dimensions of several millimeters, but is less accurate at higher frequencies (due to parasitic capacitances associated with the inductance). Accurate simulations must take into account these parasitic capacitances. Typical microstrip inductance models are in either a T or π format (Fig. 1). For the purpose of using transmission lines as inductors, the π model is a more useful representation. The following equations derive the inductance of interest. It starts with calculating the B parameter of the ABCD matrix from the two-port S-parameters, and then calculating Y3 from the inverse of B. Finally, resistance and inductance are derived from Y3. The shunt capacitance from Y1 and Y2 can be derived with similar equations (not listed here):

With the continuously shrinking size of cellular phones, Personal Digital Assistants (PDAs), and other wireless devices, the circuit-board area left over for the PAM is reduced with each generation. This requires components such as the PAM to be no larger than a few tens of square millimeters. This can be done by shrinking the semiconductor die, using smaller (0201 sized) lumped circuit elements, and reducing the substrate size. Typical transmission lines with only one upper-layer metal and one ground plane become too large for the available space. But the overlay-inductor approach, often used in RF ICs, may be useful. Such inductors have multiple layers in spiral form. Mutual coupling increases the inductance value in a relatively small area. As modeled with the Advanced Design System (ADS) software (Fig. 2) from Agilent Technologies (Santa Rosa, CA), an overlay inductor with a length of 1000 µm for each layer equals the inductance of a single-layer microstrip inductor 4600 µm long, with loss of only 0.09 O for the overlay inductor compared to 0.16 O for the microstrip inductor.

The two inductors have the same dielectric constants and total thickness. In other words, if occupying the same board area, a two-layer overlay inductor has four times the inductance as a single-layer inductor, depending on the stack up of the substrate. The closer the two signal layers are, the higher the inductance from higher coupling. The height of the second metal layer above the ground plane is also proportional to the increase of inductance, but will limit the loss performance.

Effective PAM output matching network design can deliver a target output-power goal while also improving the PAE. In many PAM designs, the input matching and interstage matching networks are mostly integrated on the semiconductor die, so the design of the output matching network is most critical. Several types of output matching networks are typically used for cellular PAMs, including bandpass, highpass, and lowpass approaches. The lowpass method is the most widely used, since it requires few components and provides good harmonic rejection. Figure 3 shows a lowpass matching network consisting of two lowpass filters, a DC blocking capacitor, a RF choke inductor, and a bypass capacitor. This circuit is for GSM850/900 band applications. For single-band applications, often only one lowpass filter section is needed.

A three-dimensional drawing is helpful in visualizing the multilayer structure of a PAM output-matching network with two overlay inductors (Fig. 4). In this practical design, the second serial inductor for the lowpass network and the RF choke are overlay inductors. Since only a few tens of nanoHenrys of inductance are needed for the first serial inductor and the two harmonic shunt inductors; they can be fabricated with single-layer microstrip. Figure 4 shows two circuit layers and a ground layer; for clarity, the ground viaholes are not shown. The top metal of the substrate stack and the overlay line are shown in green while the second layer is shown in brown.

To compare the two matching approaches, an overlay-inductor matching network and a single-layer microstrip inductor matching network were both terminated to the same PA die. When tuned with equal power out, the overlay method improves efficiency in EGSM band by 3 to 4 percent compared to the single-layer approach (Fig. 5). Figure 6 shows the PAE performance of a final design (a TQM7M4006 module) incorporating the overlay-inductor matching network.

The TQM7M4006 GSM PAM includes a CMOS power control die, two InGaP GaAs (GSM 850/900 and DCS1800/PCS1900) PA die, a GaAs passive output matching die, and two surface-mount devices. TriQuint's CuFlip™ flip-chip process enables the high density assembly necessitated by the PAM's 5 × 5-mm form factor.

The TQM7M4006 achieves PAE of 54 percent (at 850 MHz), 58 percent (at 900 MHz) and 51 percent (at 1800 and 1900 MHz) while delivering output power of +35 dBm (GSM 850/900) and +33 dBm (1800 MHz/1900 MHz). The table collects key specifications for the TQM7M4006 PAM. Undesired coupling was minimized by attention to detail (and proper spacing of lines) in the module layout. This allows the PAM to achieve stability at load mismatches of 8:1 with −20 dBm GSM to DCS/PCS crosstalk. The GSM PAM is capable of withstanding 10:1 mismatch at the output port, while delivering maximum output power. The PAM is designed for good isolation with dynamic range of 55 dB (−20 to +35 dBm) for GSM 850/900 and 53 dB (−20 to +33 dBm) for DCS/PCS.

ACKNOWLEDGMENTS

The authors would like to thank Tom Apel and Ed Knapp for some good discussion on the overlay inductor concept and impedance matching network, as well as Matt Salove, Steve LeSage, and Tim McCune for their support during the project.

REFERENCES

- Chris Bowick, "RF Circuit Design," Newnes, 1997.

- David M. Pozar, Microwave Engineering, Addison-Wesley Publishing Co., September 1993.

- E. Olsen, "HBT Power Amplifier Serves CDMA Needs," Microwaves & RF, Vol. 39, No. 4, April 2000.

- J.X. Deng, P. Gudem, "A High-Efficiency SiGe BiCMOS WCDMA Power Amplifier with Dynamic Current Biasing for Improved Average Efficiency," 2004 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium.

- Tsang-Yen Hsieh and Nai-Chueh Wang, "A GSM Standard Band Selective Repeater," Microwave Journal, Vol. 46, No. 5, May 2003.