Low-noise-amplifier (LNA) design requires tradeoffs, often among such goals as noise figure, gain, linearity, and stability. In addition, portable applications call for low power consumption. But through the use of a common- gate (CG) architecture for input impedance matching and reduced power consumption through currentreuse techniques, an RF CMOS LNA was developed with 15.5-dB forward gain and 1.68 dB noise figure at 2.4 GHz. With its excellent input and output impedance matching, it consumes only 1.05 mW power.

Low-voltage and current-reuse design approaches can effectively decrease power consumption,1-9 including the use of cascode amplifier configurations.1-4 With the currentreuse topology, desirable gain can be achieved with relatively low current consumption. However, due to the use of multiple transistors, it employs increased supply voltage. To lower the supply voltage, a folded topology has been proposed.5,6 The required supply voltage is reduced by one transistor compared with that of a cascade amplifier. Unfortunately, with more than one gain stage, the total current consumption of a CMOS LNA may not be minimized. A current-reuse, two-stage common-source (CS) topology can provide high gain at low supply voltage and power consumption, although at somewhat elevated noise levels.7-9 With a current-reuse, two-stage CG topology, however, both high gain and low noise figure can be achieved at low voltages and power consumption.

The inductor-degenerated CS topology is a popular LNA choice for narrowband applications; it provides both high gain and relatively low noise figure. But it provides low noise figure via high power consumption and/or high-quality-factor (high-Q) off-chip inductors. The noise figure of these structures increases sharply as the power consumption is decreased. 13 For a low-power receiver, an LNA based on a CG approach is the preferred topology.11 At 2.4 GHz, CG LNAs typically offer lower noise figures than CS LNAs for power consumption below 3.1 mW.12 Compared to CS LNAs, CG LNAs feature broadband input match and better linearity and stability.13 To achieve a low noise figure with low power consumption, a CG LNA input structure was used (Fig. 1); by tuning input inductor LS and capacitor C1, the noise figure can be reduced to minimum. In addition, this structure's current-reuse two-stage topology provides relatively high gain with reduced power consumption.

In Fig.1, CS MOS transistors M1 and M2 represent the first and second stages, respectively, of the LNA. They share the same DC bias current flowing through L1 to reduce power consumption. The amplified RF signal from M1 is directed to the gate node of M2through coupling capacitor C4. Capacitor C3 is the RF bypass for M2. Inductor LS and capacitor C1 help to obtain simultaneous power and noise matching for the input stage, while output matching is provided by Ld, C2, and C5. The LC network L1-C4 between the gain stages is used for interstage matching.

The proposed LNA topology is basically a two-stage amplifier (Fig. 2). The overall transconductance is equal to the multiplication of the individual transconductances of devices M2 and M2. Therefore, it has a comparable power gain to the cascaded CS amplifier topology.

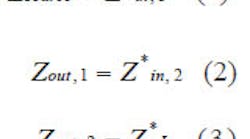

The input of the LNA must be matched to the output of the filter following the antenna to minimize reflections between the LNA and the antenna. The proposed LNA is treated as a two-stage amplifier, with simplified circuit model in Fig. 2. The conditions for input matching7 are shown in Eqs. 1-3:

where Zsource is the impedance seen at the gate of M1 when looking toward the antenna,

Zin,1 is the input impedance of M1, and ZL is the load impedance.

A simple, small-signal equivalent circuit of the first gain stage is illustrated in Fig. 3 where RS is the source impedance, and gm represents the transconductance of the MOSFETs. In Fig. 3, the input impedance of M1, Zin, is expressed by Eq. 4:

From Eq. 4, the input impedance matching to a 50-Ohm system can be achieved by

From Eqs. 5 and 6, the operating frequency, ?0, can be derived as

From the input matching conditions described in Eqs. 1-3, the effective transconductance of the first stage, gM1,eff, can be written as:

where s = j?0 and gM1 is the transconductance of M1. From Eqs. 1-3, it is possible to also know the effective transconductance of the second stage, gM2,eff, as

where gM2 is the transconductance of M2 and Cgs2 is the gate-to-source capacitance of M2. The overall effective transconductance is equal to the multiplication of the individual transconductance of M1 and M2. Therefore, two cascaded stages are employed in the proposed LNA topology to boost the amplifier gain for ultra-low-voltage operation.

As the first active building block in an RF receiver, the LNA is required to provide sufficient gain such that the noise contributed from the following stages can be effectively suppressed. In a cascade amplifier, the total noise figure can be expressed14 by Eq. 10:

where NFn and Gn are the noise figure and gain of the nth stage, respectively. According to Eq. 10, the noise figure and gain of the first stage are both very important for total noise figure contribution. Thus, the first stage should be carefully designed to achieve a good input matching and to make a tradeoff among gain, noise figure, and power consumption.

The noise factor of a two-port network, such as the LNA, can be expressed1 as Eq. 11:

where Fmin is the minimum noise factor, Gn is the equivalent noise conductance, Zsource = Rsource + jXsource is the impedance seen at the input of the LNA when looking toward the antenna, and Zopt = Ropt + jXopt is the optimum source impedance. Although Fmin can be minimized by properly choosing the width of the MOS device, this is not a good choice for constant DC current. To minimize the NF, , it is crucial to design the matching network of the LNA such that the second term in Eq. 14 is close to zero, which in turn means that Zsource should be close to Zopt.

The matching conditions for minimum noise figures of the cascaded gain stages7 are given by Eq. 12:

with the matching conditions specified in Eqs. 1-3 and 12 resulting in

From Eq. 13, this yields

From Fig. 2, the relations of Eqs. 16 and 17 can be found:

According to the definition of a matching network, the noise and power matching of the LNA are achieved when Eqs. 14 and 15 are satisfied. Therefore, when Ropt is larger than Rin,1, there is a tradeoff between the noise figure and S11. Using a CS LNA configuration with inductive degeneration for input matching, power and noise matching cannot be obtained simultaneously at low current bias, thus the noise figure could be potentially high for low-power applications. For a low-power LNA, a CG LNA is the preferred topology.

In the proposed LNA, even when the MOSFET's Ropt is larger than Rin,1, from Eqs. 16 and 17, it is possible to adjust the sizes of M1, LS , and C1 to achieve optimum input matching and noise matching simultaneously. In addition, a value of S11 of less than -10 dB is adequate for an LNA in most applications.1 Therefore, the value of Rsource can be brought much closer to the value of Ropt by altering the values of LS and C1 for better noise matching, while S11 is less than -10 dB. Noise figure responses with various values of LS and C1 are shown in Figs. 4(a) and 4(b), respectively, indicating that is it possible to reduce the noise figure as low as possible by adjusting the values of LS and C1. With shunt capacitance C1, the value of LS can be decreased to a level suitable for on-chip integration.

Continue to page 2

Page Title

Circuit simulations for the proposed design were performed with the Advanced Design System (ADS) suite of software tools from Agilent Technologies. Measured S-parameters are shown in Fig. 5 for comparison. The maximal power gain is 15.5 dB at 2.4 GHz, S11 is -10.5 dB at 2.4 GHz, and S22 is -12.3 dB at 2.4 GHz. The measured noise figure reaches 1.68 dB at 2.4 GHz. The LNA's measured input third-order intercept (IIP3) is -6.5 dBm. The DC power consumption is only 1.05 mW from a 0.9-V supply.

A commonly used figure of merit (FOM) for comparing low-power LNAs is the ratio of power gain to DC power consumption (gain/DC power). A more meaningful FOM includes the effects of amplifier gain, noise figure, linearity (IIP3), operating frequency (f0), and DC power consumption (Pdc)15 as shown in Eq. 18.

The table shows data from a number of low-power CMOS LNAs. It shows that this ultra-low-power LNA can provide better overall performance in terms of gain, noise figure, linearity, DC power consumption, and frequency of operation. The LNA was fabricated with a standard 0.18- m CMOS technology and offers the best gain to DC power ratio and overall FOM among recently published low-power CMOS LNAs.

REFERENCES

1. Saman Asgaran and M. Jamal Deen, "Design of the Input Matching Network of RF CMOS LNAs for Low-Power Operation," IEEE Transactions On Circuits And Systems, Vol. 54, No. 3, March 2007, pp. 544-554.

2. Majid El Kaamouchi and Mehdi Si Moussa, "A 2.4-GHz Fully Integrated ESD-Protected Low-Noise Amplifier in 130-nm PD SOI CMOS Technology," IEEE Transactions On Microwave Theory And Techniques, Vol. 55, No. 12, December 2007, pp. 2822-2831.

3. Mikal Cimino and Herv Lapuyade, "Design of a 0.9-V, 2.45-GHz Self- Testable and Reliability-Enhanced CMOS LNA," IEEE Journal Of Solid- State Circuits, Vol. 43, No. 5, May 2008, pp. 1187-1194.

4. Yiping Feng, Gaku Takemura, Shunji Kawaguchi, and Peter Kinget. "Design of a High Performance 2-GHz Direct-Conversion Front-End With a Single-Ended RF Input in 0.13-m CMOS," IEEE Journal Of Solid-State Circuits, Vol. 44, No. 5, May 2009, pp. 1380-1390.

5. Hsieh-Hung Hsieh, "Gain-Enhancement Techniques for CMOS Folded Cascode LNAs at Low-Voltage Operations," IEEE Trans. Microwave Theory And Techniques, Vol. 56, No. 8, August 2008, pp. 1807-1816.

6. Dake Wu, "A 0.4-V Low Noise Amplifier Using Forward Body Bias Technology for 5 GHz Application," IEEE Microwave And Wireless Components Letters, Vol. 17, No. 7, July 2007, pp. 543-545.

7. Hsieh-Hung Hsieh, "Design of Ultra-Low-Voltage RF Front-ends With Complementary Current-Reused Architectures," IEEE Trans. Microwave Theory And Techniques, Vol. 55, No. 7, July 2007, pp. 1445-1458.

8. Muh-Dey Wei, "A Low-Power Ultra-Compact CMOS LNA with Shunt- Resonating Current-Reused Topology," IEEE Third European Microwave Integrated Circuits Conference, October, 2008, pp. 350-353.

9. Chen-Yuan Chu and Chien-Cheng Wei. A 24GHz Low-Power CMOS Receiver Design. Circuits and system, 2008.ISCAS 2008.IEEE International symposium on 18-21 May 2008.p.980-983.

10. Jere A. M. Jrvinen, Jouni Kaukovuori, and Jussi Ryynnen, "2.4-GHz Receiver for Sensor Applications," IEEE Journal Of Solid-State Circuits, Vol. 40, No. 7, July 2005, pp. 1426-1433.

11. Wenjian Chen, Tino Copani, Hugh J. Barnaby, and Sayfe Kiaei, "A 0.13- m CMOS Ultra-Low Power Front-End Receiver for Wireless Sensor Networks," 2007 IEEE RF Integrated Circuits Symposium, pp.105-108.

12. James Ayers, Kartikeya Mayaram, and Terri S. Fiez, "Tradeoffs in the Design of CMOS Receivers for Low Power Wireless Sensor Networks, Circuits, and Systems," ISCAS 2007, IEEE International Symposium, May 27-30, 2007, pp. 1345-1348.

13. Saeed Sarhangian and S. Mojtaba Atarodi, "A Low-Power CMOS Low-IF Receiver Front-End for 2450-MHz Band IEEE 802.15.4 ZigBee Standard," Circuits and Systems, ISCAS 2007, IEEE Int. Symp., May 27-30, 2007, pp. 433-436.

14. Da-Ke Wu, Ru Huang, and Yang-Yuan Wang, "A Low-Voltage and Low-Power CMOS LNA Using Forward-Body-Bias NMOS at 5 GHz," 2006 Solid-State and Integrated Circuit Technology, ICSICT 2006, 8th International Conference, pp. 1658-1660.

15. Hanil Lee and Saeed Mohammadi, "A 3-GHz Subthreshold CMOS Low Noise Amplifier," 2006 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, June 11-13, 2006, p. 4.