Ultrawideband (UWB) communications systems can operate with a variety of modulation formats in the bandwidth allocated by the United States Federal Communications Commission (FCC) from 3.1 to 10.6 GHz. In all cases, a broadband low-noise amplifier (LNA) is essential to the receiver, with low DC power consumption. One solution is a low-voltage variable-gain CMOS design capable of 14-dB gain from 3.1 to 10.6 GHz with minimal noise figure of 3.2 dB.

Although different wideband pulse shapes and pulse modulation schemes have been proposed for future UWB transmission systems, two major proposals are now the candidatures for the IEEE 802.15.3 standard1: the direct sequence (DS)-UWB2 approach and the multi-band orthogonal frequency- division-multiplex (OFDM) UWB approach.3 A wideband LNA is an important building block in an UWB receiver. A number of low-noise designs have been developed based on silicon CMOS device technology.4-8

However, conventional UWB LNAs cannot provide the variable-gain function. A variable-gain LNA (VG LNA) not only can prevent a receiver from saturation when the input signal is relatively large, but also can mitigate the linearity requirement of the following mixer and maximize the dynamic range of the overall system.9 A number of UWB VG LNAs have been reported in the literature. For example, several researchers proposed a distributed VG LNA.10 The main advantages of the distributed amplifier are its intrinsic broadband characteristic, good input and output matching, however, the power consumption is high and the chip area is relatively large. Other researchers proposed a VG LNA with broad bandwidth and good gain flatness, however, the gain and gain-variable range was limited and the power consumption is relatively high.11

To meet the conditions for broadband impedance matching from 3.1 to 10.6 GHz with adequate variablegain range, an amplifier was designed based on a common-gate transistor as the input stage. The LNA uses a modified cascade structure aimed at low power consumption. The commongate stage and its associated small-signal circuitry9 is shown in Fig. 1. Source inductor LS is placed between the source of the metal-oxide-semiconductor (MOS) transistor to form an inductive-capacitive (LC) resonator with gate-to-source capacitance, Cgs. As reference 12 points out, the finite output resistance of the transistor also influences LNA performance, since the load impedance of the commongate stage and the input impedance of the next stage degrade impedance matching and noise performance due to the short-channel MOS transistor's low output resistance, about 500 O for an 0.18-μm CMOS process.13

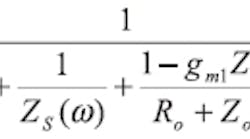

From ref. 9, the input impedance can be written as Eq. 1:

where ZS(?) and Z0(?) are given by Eqs. 2 and 3, respectively,

where ZL = the impedance of the load,

Zin2 = the input impedance of the next stage, and

gm1 = the transconductance of the MOS transistor in a common-gate configuration.

Assuming that both ZS(?) and Z0(?) are composed of high-quality-factor (high-Q) inductors and capacitors and thus can be regarded as purely reactive within the frequency band of interest:

and Eq. 1 can be rewritten by substituting in Eqs. 4 and 5 to get Eq. 6.

The term 1/XS(?) in Eq. 6 dominates the imaginary part because gm1R0X0(?)

<< R02 + X02(?) throughout the UWB frequency band. Given that gm1X0(?)

<< R20 + X20(?), the real part in the denominator will remain constant across the 3.1-to-10.6-GHz range.

As is well known, lowering the supply voltage is an effective way to reducing power consumption. Still, it is difficult to reduce the power supply of a cascade topology to under 1 V.5,8 To meet requirements for high gain, low noise figure, and low power consumption, the classical cascade topology has often been modified.14 In the current report, the structure has been modified from a narrowband circuit to one for use in ultrawideband applications.

When the cascade configuration is changed to a parallel topology, the current is no longer reused by the common- gate stage and common-source stage. This lack of reuse will result in an increase in DC power consumption. In order to minimize the use of bias current, a current mirror is added to the common-source stage. At the same time, a resistor is added to the source of the common-gate stage to control the DC current.

In the cascode topology, the common- gate transistor (M3 in Fig. 3) can be used to improve power gain and achieve variable gain control without influencing input and output match. The common-gate configuration is also used to enhance the reverse isolation and high-frequency response, and restrain the Miller effect. The power gain for this stage is expressed as Eq. 7, where

gm2 = the transconductance of M2;

gm3 = the transconductance of M3; and

CD3 = the total parasitic capacitances at the drain of transistor M3.

Equation 7 shows that the gain is proportional to gm2. gm2 and ID can be written as Eqs. 8 and 9:

where

K = a transconductance parameter;

W = the width of M2 and M3;

L = the length of M2 and M3;

ID = the DC drain current of the second stage;

? = the channel length modulation parameter of transistors M2 and M3;

Vds2 = the drain-source voltage of transistor M2; and

Vgs2 = the gate-source voltage of M2.

Continue on page 2

Page Title

In fact, transistor M3 can be seen as the load of transistor M2. It has impedance of Zds3. When VC is increased, from Eqs. 8 and 9 it can be seen that ID would increase because impedance Zds3 would decrease as VC increases and Vds2 is also increased; thus transconductance gm2 is also increased. From these relationships, it can be concluded that gain can be controlled by varying VCsee Fig. 2(a)>.

For a cascade system, the noise figure of the first stage is critical to the whole circuit, especially when the common-gate stage is employed for UWB input matching. The commongate configuration is generally noisier than narrowband matching techniques such as inductive source degeneration. The noise factor of the common-gate stage can be written as12:

where c = the correlation coefficient,

and theoretically c = -0.395j for longchannel devices. Additional parameters, a and d, are process constants.

As gm1 appears in the denominators of all noise components, it can be increased (by reducing Rref1 in Fig. 3) to improve the overall noise performance. However, the input matching degrades as gm1 increases see Fig. 2(b)>.

In the circuit design, a large (1-pF) capacitor (C1 in Fig. 1) is placed between the gate of transistor M1 and ground, for two reasons. This ensures good AC grounding and bypasses the noise contributed by the biasing circuit. Also, with the drain-gate capacitance of transistor M1, this forms a noiseless capacitive divider as a feedback network.15 The design of the proposed variable-gain LNA is based on an 0.18-μm RF CMOS process from TSMC. All transistors employ the minimum gate length of 0.18 μm for minimum parasitic capacitance. According to ref. 16, the optimized gate width for transistor M1 is 100 μm. Simulations show that the best input matching impedance is achieved with a source inductance, LS, of 6.9 nH.

In the circuit, current mirrors have been added for M2 and M4. By adjusting the value of reference resistor Rref2, bias current is set to 2 mA. The gate widths of transistors M2 through M5 are also set to 100 μm. A resistance of 200 O is chosen for source resistor RS so that currents of M2 and M5 are both set to 2 mA. The gate width of M9 and M10 is selected as 10 μm. A buffer is added at the output to drive output test equipment and also output pad capacitance. It is composed of transistors M6 and M7. The output impedance is designed to be 50 O for desired output impedance matching. The parasitic capacitance of M4 serves as the load of the UWB LNA, which emulates the input impedance of the connected mixer in the system. The gate widths are 30 m for M6 and 60 m for M7. M6 was sized at one-half the size of M7 to save DC current.

Computer-aided-engineering (CAE) software from Cadence Design Systems was used to simulate the circuit, as shown in Figs. 4 through 7. The input and output reflection coefficients were maintained below -10 dB from 3.1 to 10.6 GHz (Fig. 5). Figures 4 and 5 show the pre-layout and post-layout simulation results for forward transmission, S21. The results show that S21 dropped from 20 dB to 14 dB, within 0.4 dB, from 3.1 to 10.6 GHz. This is because the parasitic resistors and capacitors degrade the power gain, especially at higher frequencies. The minimum noise figure is 3.2 dB (Fig. 6), while S12 drops below -75 dB in the UWB band, indicating good reverse isolation (Fig. 7). The average noise figure is 5.8 dB. The LNA has a 1-dB compression point of -37 dBm for a die size of 1.3 x 0.73 mm, including pads and guard ring. DC power consumption is 10 mW, including the buffer, for a supply voltage of +0.85 VDC. The table compares this LNA with recently reported LNAs.

ACKNOWLEDGMENTS

This work was supported by the Open Fund Project of the Key Laboratory of Hunan Universities, Hunan, China, (grant No. 09K011) and in part by the National Natural Science Foundation of China (grant No. 60776021).

REFERENCES

1. IEEE 802.15 WPAN High Rate Alternative PHY Task Group 3a (TG3a), report available at: www.ieee802.org/15/pub/TG3a. html.

2. "Multi-band OFDM Physical Layer Proposal update," IEEE P802.15 Working Group for Wireless Personal Area Networks (WPANs), PowerPoint presentation available at: grouper.ieee.org/groups/802/15/pub/04/15-04-0122-00-003a-15-04-0122-00-003amulti-band-ofdm-mar04-update.ppt.

3. "DS-UWB Proposal update," IEEE P802.15 Working Group for Wireless Personal Area Networks, PowerPoint presentation available at: grouper.ieee.org/groups/802/15/pub/04/15-04-0140-02-003a-merger%232-proposal-ds-uwb-presentation.ppt.

4. R. Liu, C. Lin, K. Deng, and H.Wang, "A 0.514-GHz 10.6-dB CMOS cascode distributed amplifier," in Digest of the Symposium on VLSI Circuits, June 2003, Vol. 17, pp. 139140.

5. C. F. Liao and S. I. Liu, "A broadband noise-canceling CMOS LNA for 3.110.6-GHz UWB receiver," in Proceedings of the IEEE 2005 Custom Integrated Circuits Conference, September 2005, pp. 161164.

6. C.-W. Kim, M.-S. Kang, P. T. Anh, H.-T. Kim, and S.-G. Lee, "An ultra wide-band CMOS lownoise amplifier for 35-GHz UWB system," IEEE Journal of Solid-State Circuits, Vol. 40, No. 2, pp. 544547, February 2005.

7. F. Zhang and P. Kinget, "Low power programmable-gain CMOS distributed LNA for ultra-wide-band applications," in Digest of Technical Papers Symposium VLSI Circuits, 2005, pp. 7881.

8. A. Bevilacqua and A. M. Niknejad, "An ultra-wide-band CMOS low noise amplifier for 3.1 to 10.6-GHz wireless receiver," IEEE Journal of Solid-State Circuits, Vol. 39, No. 12, December 2004, pp. 22592268.

9. Y. Aoki, M. Fujii, S. Ohkubo, S. Yoshida, T. Niwa, Y. Miyoshi, H. Dodo, and H. Hida, "A 1.4-dB-NF variable gain LNA with continuous control for 2 GHz band mobile phones using InGaP emitter HBTs," in IEEE RFIC Symposium Digest, 2001, pp. 231234.

10. F. Zhang and P. Kinget, "Low power programmable-gain CMOS distributed LNA for ultrawideband applications," iEEE Symp. VLSI Circuits Technical Digest, 2005, pp. 7881.

11. Yang Kai, Wang Chunhua, Dai Puxing. "A new CMOS continuous variable gain LNA for 3~10 GHz UWB wireless receivers," Frequenz, 2008.12

12. Y. Lu, K. S. Yeo, A. Cabuk, J. Ma, M. A. Do, and Z. Lu, "A novel CMOS low-noise amplifier design for 3.1-to-10.6-GHz ultra-wideband wireless receiver," IEEE Transactions on Circuits and Systems I, Regular Papers, Vol. 53, No. 8, August 2006, pp. 16831692.

13. C.-H. Chen, M. J. Deen, Y. Cheng, and M. Matloubian, "Extraction of the induced gate noise, channel noise, and their correlation in submicron MOSFETs from RF noise measurements," IEEE Transactions on Electron Devices, Vol. 48, No. 12, 2001, pp. 28842892.

14. M. Z. Khan, "A 0.65-V, 2.4-GHz CMOS low-noise amplifier design with noise optimization," Canadian Conf. on Electrical and Computer Engineering, Canada.2005.673- 676.

15. G. Cusmai, "A 0.18-μm CMOS Selective Receiver Front-End for UWB Applications," IEEE Journal of Solid-State Circuits, Vol. 41, No. 8, 2006, pp. 1764- 1771.

16. Lee Thomas, The Design of CMOS Radio Frequency Integrated Circuits, Cambridge University Press, Cambridge, England, 1998.

17. Chang-Ching Wu, Albert Yen, Yu Cheng, and Jen-Chung Chang: "A Switched Gain Low Noise Amplifier for Ultra-wideband Wireless Applications", Radio and Wireless Symposium, IEEE, 2007-01, pp. 193-196.

18. Yanxin Wang, J. S. Duster, and K. T. Kornegay, "Design of an ultra-wideband low noise amplifier in 0.13-μm CMOS, Circuits and Systems 2005, ISCAS 2005, IEEE International Symposium, pp. 5067-5070.

19. S. Vishwakarma, Sungyong Jung, and Youngjoong Joo, "Ultra wideband CMOS low noise amplifier with active input matching," Ultra-wideband Systems 2004, Joint with Conference on Ultra-wideband Systems and Technologies, Joint UWBST & IWUWBS, 2004 International Workshop, 2004-2005, pp. 415-419.