Low-noise amplifiers (LNAs) are vital to the receivers in most wireless applications, although a common design challenge is to achieve high small-signal gain while also attaining low noise figure. LNAs can be constructed in a number of ways, including as voltage-mode amplifiers or as current-mode amplifiers. To demonstrate the effectiveness of the latter approach, a high-gain current-mode LNA with low noise figure was designed for use in IEEE 802.11a wireless local area network (WLAN) applications at 5.8 GHz. The two-stage amplifier employs an inductive-capacitive (LC) network to eliminate the need for a source inductor; it also features an NMOS current mirror using an inductive series peaking technique to achieve optimized current output and high gain. Simulated results reveal 18.52 dB transconductance gain at 5.8 GHz, with noise figure of 0.93 dB and power consumption of only 4.9 mW.

Conventional voltage-mode LNAs can suffer many drawbacks, including limited bandwidth, the need for a high voltage supply, and the requirement for a current-to-voltage transconductance stage due to the presence of high-impedance nodes. In contrast, current-mode LNAs offer many advantages over voltage-mode LNAs, including wide bandwidth, low supply voltage requirements, tunable input impedances, and less susceptibility to power and ground fluctuations.1 Although some articles about IEEE 802.11a LNAs have been written in recent years,1-7 few have covered current-mode designs. The IEEE 802.11a standard, based on orthogonal-frequency-division-multiplexing (OFDM) modulation, provides nearly 5 times the data rate and as much as 10 times the system capacity as IEEE 802.11b and 802.11g systems.

In support of the IEEE 802.11a standard, a novel current-mode LNA sans source-degrading inductor was developed. The two-stage design employs a NMOS current mirror for high gain with low noise figure and good impedance matching. Compared with previous LNAs designed for the same frequency3,6 and nearby frequencies,4,5,7 the proposed LNA offers higher transconductance gain of 18.52 dB and much lower noise figure of 0.93 dB. It also consumes only 4.9 mW at 850 mV.

Figure 1 shows the circuit diagram for the novel current-model LNA, including its biasing circuitry. The first stage is a common-source configuration that uses a shunt-peaking technique to achieve high gain with low noise figure. The second stage is a cascode structure that provides the properties of high gain, low noise, and high reverse isolation. Transistor M4 is used for good reverse isolation and to restrict the Miller effect. The last stage, the current mirror with inductive peaking, helps realize good output impedance matching.8

Conventional common-source LNA structures often rely on a source degeneration inductor to achieve simultaneous low noise figure and power matching, but typically sacrifice gain and noise-figure performance levels in the process.9 The structure presented in this circuit does not include the degeneration inductor. Rather, it uses a LC network at the gate terminal of the common-source stage to eliminate the source degeneration inductor. In doing so, it achieves improved gain with reduced noise, also reducing chip area and dropping the cost when fabricated in a semiconductor process. Circuit elements L1, C1, and C2 are used to implement the LC network.10 The circuits composed of L2 adopting shunt-peaking technique are used to resonate with the gate-source capacitor, Cgs, of M1 to achieve high gain at 5.8 GHz. Capacitors C3 and C4 are added for DC signal choking.

A current mirror formed of circuit elements M2, R2, and R3 is used as a biasing circuit for transistor M3, while circuit elements M2, R2, and R4 form the current mirror used as a biasing circuit for M4. The width of device M2 is reduced to minimize power consumption. Resistors R2, R3, and R4 are added for signal choking; they are selected for large values so that their noise contributions can be neglected.6,11

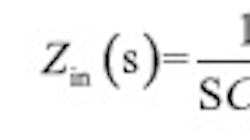

Figure 2 shows the input stage of the proposed LNA. Transistor M1 is operated in its saturation region. Impedance, Zin(s) of the input stage of the proposed LNA, can be expressed as Eq. 1:

where:

Cgs1 = the gate-source capacitance of transistor M1.

Figure 3 shows a small-signal model of the input stage of the proposed LNA. The gain of the input stage can be found through analysis, as shown in Eq. 2:

where:

gm1 = the transconductance of transistor M1.

The cascade second stage of the LNA includes M3, M4, L3, and its biasing circuit. The cascode stage biasing circuit is a current mirror composed of M2, R2, and R3. Figure 4 shows a small-signal model of the proposed LNA's cascode stage.

According to the Miller Theorem, gate-source capacitance Cgs can be divided into capacitances Ca and Cb, as shown by Eqs. 3-5:

k = -gm3/gm4 (3)

Ca = Ggd3(1 - k) (4)

Cb = Ggd3(1 - k) (5)

According to the Kirchhoff Theorem, at the G1 terminal, there would be:

See Eq. 6.

and at the D1 terminal:

See Eq. 9.

When gm3 = gm4, then k = -gm3/gm4 = -1; Ca = Cgd3(1 - k) = 2Cgd3; and Cb = Cgd3/(1 - k) = Cgd3/2.

If the partial capacitances Ca and Cb are substituted into Eq. 10, then Eq. 10 appears like so.

See Eq. 10.

In this circuit, ZL1 = sL2. By adjusting the ratio of the width to length for devices M1 and M3, it is possible to achieve high values for gm1 and gm3, respectively, making it possible to achieve high gains for the LNA's first and second stages. Inductor L1 has also been adjusted considering the balance between the input impedance matching and the gain.

Figure 4 shows the current mirror used in the three-stage LNA, with inductive series peaking. When the channel length modulation and the high-order effects of MOS transistors are neglected, the basic current amplifier shown in Fig.4 with Lgg = 0 has a DC current gain of A -gm6/gm5, where gmk is the transconductance of transistor Mk. If a compensation inductor is placed in series with capacitance Cgs2 (as shown in Fig. 5), with the assumption that Cgs6 >> Cgs5, the transfer function of the current mirror can be given by Eq. 11.

See Eq. 11.

The series inductance was added to the NMOS current mirror to improve the amplifier's high-frequency performance. From Eq. 11, it can be seen that additional inductor Lgg does not affect the DC characteristics of the current mirror, but does improve the high-frequency characteristics and enhance the amplifier's wideband performance. By combining Eqs. 2 and 11, the transconductance gain of the current-mode LNA can be found from Eq. 12.

See Eq. 12.

Since an LNA is the first component block in a receiver, its noise figure will impact the overall performance of the receiver. A well-designed LNA should exhibit a noise figure of less than 3 dB.12 For the proposed LNA, the noise performance is mainly determined by two factors: the loss of the input network and the noise of input stage M1. For the proposed LNA, the optimized noise figure of the first stage can be found from Eq. 1313:

while the optimized gate width of M1 is shown by Eq. 14:

where:

a = a constant;

Cox = the gate oxide capacitance per unit area;

Leff = the effective gate length; and

Qsp = the best quality factor, ranging from 3.5 to 5.5, as shown by Eq. 15.

See Eq. 15.

Noise in the LNA's second stage is contributed mainly by transistor M3, according to Eq. 16.

where:

gm3 = the transconductance of transistor M3, and

Rs3 = the equivalent source impedance of M3.

By optimizing the gate width of M1, the noise figure of the LNA's first stage has also been optimized. Since it is a common-source stage with high gain, the value of Ap1 is also high. By adjusting the width and the length of M3, a relatively high value of gm3 can be achieved, as can the low noise figure of the second stage. By combining the factors mentioned above, the circuit total noise figure can be found by Eq. 17.

See Eq. 17.

The proposed LNA was simulated with the aid of Cadence SpectreRF software from Cadence Design Systems based on 0.18-m RF CMOS semiconductor process parameters. A symmetrical layout was employed to minimize mismatches as much as possible. Figure 6 shows a simulation of transconductance gain, which was 18.52 dB at 5.8 GHz. Figure 7 shows the simulated noise figure, 0.93 dB at 5.8 GHz. Figure 8 shows that the simulated S11 performance is -11.48 dB at 5.8 GHz, indicating good input match. Figure 9 offers the LNA's simulated S22 performance, with return loss of 10.21 dB following optimized output matching. The power dissipation is 4.9 mW from a 0.85 V supply voltage. The layout diagram of the circuit is shown in Fig. 10, which takes a compact chip area of 0.9 0.8 mm.

The table compares the simulated performance levels of the proposed LNA with other published efforts. it can be seen that the proposed LNA has advantages of higher transconductance gain, lower noise figure, and lower power consumption compared to other LNAs at 5.8 GHz or at nearby frequencies.

In summary, this report has detailed the analysis and simulation of a 5.8-GHz LNA suitable for fabrication with a standard silicon CMOS process. The amplifier features a three-stage design, which includes a common-source structure without source degradation inductor, a cascode structure with shunt-peaking technique, and a current mirror with inductive series peaking. The LNA circuit promises high gain, low noise figure, and good impedance matching.

Acknowledgments

The authors would like to thank the National Natural Science Foundation of China for financially supporting this research under No. 60776021, and the Open Fund Project of Key Laboratory in Hunan University No.09K011 for financially supporting this research.

References

- B. Kleveland, et al., "Exploiting CMOS reverse interconnects scaling in multigigahertz amplifier and oscillator design," IEEE Journal of Solid-State Circuits, Vol. 36, No. 10, October 2001, pp. 1480-1488.

- T. Hui Teo and Yeoh Wooi Gan, "Low-power short-range radio CMOS subharmonic RF front-end using CG-CS LNA," IEEE Transactions on Circuits and Systems, 2008, pp. 658-662.

- M. Pourakbar, P. Langari, M. Dousti, F. Temcamani, B. Dracressoniere, and J. L. Gautier, "A 1.2-V Single-Stage SiGe BiCMOS Low-Noise Amplifier at 5.8 GHz for Wireless Applications," 3rd International Conference on Information and Communication Technologies, 2008, pp. 1-5.

- Jyad Kebaisy, Sven Domann, and Bernd Meinerzhagen, "A 10-mW low-noise amplifier design for 5.5-GHZ wireless communication system," Information and Communications Technologies (ICTTA), 2006, pp. 2577-2582.

- H. Chiu, Sh. Lu, and Y. Lin, "A 2.17-dB NF 5-GHz-band monolithic CMOS LNA with 10-mW DC power consumption," IEEE Transactions on Microwave Theory & Techniques, Vol. 53, 2009, pp. 813-824.

- M.N. Husain, A.R. Othman, and M.S. Johal, "Simulation of single stage cascode low noise amplifier at 5.8GHz using t-matching network," 4th International Conference on Modeling, Simulation, and Applied Optimization (ICMSAO), 2011.

- Baohong Liu and Junfa Mao, "A Low-Voltage 5.4 GHz monolithic cascode LNA using 0.18 m CMOS technology," Microwave and Optical Technology Letters, 2010, pp. 386-389.

- A. Bevilacqua and A.M. Niknejad, "An ultra-wideband CMOS LNA for 3.1 to 10.5.8-GHz wireless receivers," ISSCC Digest Technical Papers, 2006, p. 382.

- B. Mohammadi and C.A.T. Salama, "A 5.8-GHz CMOS LNA for WLAN applications," IEEE Radio Frequency Integrated Circuits Symposium, 2004, pp.113-116.

- Standard IEEE 802.11a-1999 (supplement to IEEE Standard 802.11-1999): "Information technology Telecommunications and information exchange between systems. Part 11: High-speed Physical Layer in the 5 GHz Band," IEEE, New York, 1999.

- Viswanathan Subramanian, Marko Krcmar, M. Jamal Deen, and Georg Boeck, "A 6-GHz fully integrated SiGe LNA with simplified matching circuitries," Proceedings of the First European Wireless Technology Conference, 2008, pp.17-20.

- D. Linten, et al., "A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS," IEEE Journal of Solid-State Circuits, 2005.

- Derek K. Shaeffer, Student Member, IEEE, and Thomas H. Lee, Member, IEEE, "A 1.5-V, 1.5-GHz CMOS low noise ampli?er," IEEE Journal of Solid-State Circuits, Vol. 32, No. 5, May 1997.

- Yang Lu, Kiat Seng Yeo, and Alper Cabuk, et al., "A novel CMOS low-noise amplifier design for 3.1-to-10.6-GHz ultra-wide-band wireless receivers," IEEE Transactions on Circuits and Systems, Vol. 53, No. 8, 2006, pp. 1683-1692.