Integrated Radio Transceiver Confronts Challenges from Every Corner

Download this article in PDF format.

5G communications is associated with higher levels of complexity, such as an expanded frequency spectrum, wider bandwidths, and higher channel counts. The technology will also require products with reduced size, weight, and power (SWaP), as well as lower costs. Moreover, while original equipment manufacturers (OEMs) will obviously need to support 5G networks, they still must support previous-generation 2G, 3G, and 4G communications, too. Thus, demand will ramp up for solutions that can wrestle with current, new, and legacy wireless standards.

One company, Analog Devices (ADI), developed what it describes as a “single radio platform that can handle emerging wideband applications, while delivering the high-performance required for existing applications.” Those “single radio platforms” are the ADRV9008/9 solutions, which are the latest entries to ADI’s RadioVerse RF transceiver product line (Fig. 1). The ADRV9008/9 products are not only intended for cellular applications, but also for aerospace and defense applications and test-and-measurement equipment.

1. The ADRV9009 transceiver, which has a tunable frequency range of 75 MHz to 6 GHz, is equipped to support current, new, and legacy wireless standards and more.

High integration is a key trait of the ADRV9008/9 family—the ADRV9009 transceiver itself takes the place of more than 20 discrete components. The ADRV9009 also achieves a bandwidth of 200 MHz, which is twice the bandwidth of the previous-generation AD9371. And the integrated common radio platform reduces product-development cycles and product design variations while slashing power consumption by 50% and size by 60%, according to ADI.

Additional features include local-oscillator (LO) synchronization. This simplifies digital beamforming, reducing system complexity and cost for massive multiple-input, multiple-output (M-MIMO) and phased-array radar systems. Furthermore, fast frequency hopping reduces system downtime and improves spectral efficiency and link security.

A Closer Look at the ADRV9009 and ADRV9008-1/-2

ADI offers the ADRV9009 integrated transceiver along with the ADRV9008-1 integrated receiver and ADRV9008-2 integrated transmitter. Each has a tunable frequency range of 75 MHz to 6 GHz. All three come in a 196-ball ball-grid-array (BGA) chip-scale package (CSP) that measures 12 × 12 mm.

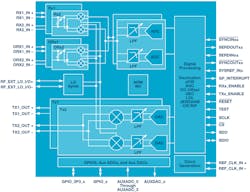

The ADRV9009 transceiver can be described as a single-chip time-division-duplex (TDD) solution. As seen in its block diagram (Fig. 2), the ADRV9009 contains two transmitters and two receivers along with two observation receivers.

2. Two transmitters, two receivers, and two observation receivers populate the ADRV9009 transceiver.

Fractional-N phased-lock-loop (PLL) frequency synthesizers are incorporated into the ADRV9009, too, as is a clock synthesizer that generates the clocks needed for the converters, digital circuits, and serial interface. And with the previously mentioned LO synchronization feature, the LOs on multiple ADRV9009 chips can be phase-synchronized to support beamforming applications.

The ADRV9009’s maximum receiver bandwidth is 200 MHz, and its maximum transmitter synthesis bandwidth is 450 MHz. Maximum observation receiver bandwidth is 450 MHz. Furthermore, the ADRV9009 utilizes a 12-Gb/s JESD204B interface.

For frequency-division-duplex (FDD) applications, ADI offers the ADRV9008-1 and ADRV9008-2. The ADRV9008-1 is an integrated dual receiver, while the ADRV9008-2 is an integrated dual transmitter and observation receiver. Together, these two devices form what ADI describes as a two-chip FDD solution.

The ADRV9008-1 has a maximum receiver bandwidth of 200 MHz. The ADRV9008-2 has a maximum transmitter synthesis bandwidth of 450 MHz and a maximum observation receiver bandwidth of 450 MHz. Both are also equipped with the LO synchronization feature, and utilize a 12-Gb/s JESD204B interface.

ADI offers various resources for its RadioVerse line, such as evaluation kits and software tools. For more information, visit www.analog.com/radioverse.