Complex modulation schemes and many other high-frequency communications applications require some form of phase detector to determine the phase and frequency of different and differential signals. Phase detectors have been available in many forms for many years, with phase-frequency detectors (PFDs) representing one of the more traditional and trusted components for detecting phase and frequency.

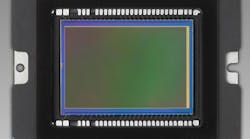

However, researchers at Universiti Kebangsaan Malaysia, Selangor, Malaysia present their work on an effective alternative approach to reading phase and frequency. This takes the form of time-to-digital converters (TDCs) which can be fabricated with silicon digital complementary-metal-oxide-semiconductor (CMOS) integrated-circuit (IC) technology to achieve small component sizes at reasonable cost.

The authors focus on the use of TDCs in all-digital phase-locked loops (ADPLLs) for stable, low-noise signal generation in modern communications systems. The use of this emerging digital phase-detection approach represents an abrupt departure from the analog phase-detection approaches that have long stabilized voltage-controlled oscillators (VCOs) and other frequency sources in PLL circuits. More mature digital phase detectors include logic-gate-based digital phase detectors and dynamic PFDs.

Since PFDs can operate in both linear and nonlinear modes, the choice of a PFD will depend a great deal upon the application. Dead zones or blind spots can exist during the normal operation of a digital PFD with a dead zone, for example, representing a region where the phase differences between two signals fed to the input of the PFD cannot be detected due to the low sensitivity of the component. For a particular PLL design, the dead zone and blind spot characteristics of a digital PFD must be carefully considered to minimize performance degradations for the PLL circuit.

Digital PFDs offer great promise for modern PLL circuits although, as with any component technology, various tradeoffs must be weighed. These include the input voltage requirements, the maximum operating speed/frequency, the detector phase/frequency sensitivity, and the power dissipation. The article reviews the use of ADPFDs in high-frequency PLLs as well as in more exotic applications, including the measurement of time for less than one clock cycle. See “Investigating Phase Detectors,” IEEE Microwave Magazine, December 2015, p. 56.

This file type includes high resolution graphics and schematics when applicable.