Sigma-Delta Synthesizer Steps Across Multiple Standards

Frequency synthesizers are fundamental building blocks in wireless systems. Market pressures drive higher levels of integration in support of multiple wireless standards. But each wireless standard requires a specific crystal reference frequency and specific channel spacing. Integer-N frequency synthesizers can achieve the small step sizes required in support of multiple standards, but with high phase noise. Fortunately, a sigma-delta fractional-N frequency synthesizer can combine the small step size with low phase noise inside the loop bandwidth, although with the cost of introducing out-of-band quantization noise. The development of a second-generation sigmadelta fractional-N frequency synthesizer, however, provides the flexibility and performance needed in a single design for multiple wireless-communications standards (refs. 1-5).

Although the sigma-delta fractional-N frequency synthesizer approach is a significant improvement over integer-N synthesizers, a sigma-delta modulator generates quantization noise outside the loop bandwidth. This unwanted noise can be filtered out by narrowing the loop bandwidth or by adding additional parasitic poles to quickly roll-off the quantization noise. Unfortunately, this requires more pins and off-chip components. More parasitic poles cause uncertainty in loop-dynamics and stability making direct modulation impractical when the desired data rates are near or above the loop bandwidth.

Frequency-switching time is also an issue in any synthesizer design for wireless standards. A synthesizer requires a narrow loop bandwidth to attenuate the out-of-band quantization noise whereas fast switching times require the synthesizer with a wide loop bandwidth. To achieve the desired switching speed and phase noise for a given standard, it is possible to use multi-state loop filters to acquire lock quickly. One state would be wideband for acquisition and the other would be narrow for phase noise. When a multi-state loop filter changes state, incorrectly charged capacitors (parasitic or intentional) can be present unless the multi-state loop filter is carefully designed. These capacitors can move the synthesizer away from the desired lock point just as it switches to a low bandwidth, making acquisition time specifications harder to meet.

Large resistors in analog loop filters add out-of-band noise to the synthesizer. Small resistor values require large capacitors to obtain the same time constants, forcing the use of off-chip capacitors. The on-resistance of switches in multi-state loop filters must be small, implying large switches. This causes more capacitive feedthrough when the filter changes state. A two-state loop filter can be challenging for even one mode of a single wireless standard, let alone for multimode use. Different standards call for different loop bandwidths and VCOs, making the challenge to bring everything on a single chip difficult.

A 2-GHz synthesizer with a 26-MHz reference frequency and a loop bandwidth of approximately 45 kHz would require the loop filter component values listed in Table 1. The loop filter components were calculated for the passive loop filter shown in Fig. 1. While resistor R1 could easily be integrated, the main capacitor C1 would require an impractical size of approximately 15 X 106 m2 (3900 X 3900 m) in a typical 0.35m BiCMOS process.

The practical requirement for having to leave loop filters off-chip results in several design issues. External components are expensive and occupy printed-circuitboard (PCB) space. The pads used to interface with off-chip components are in high demand as many chips are pad limited. Costs can be increased if additional pads force the use of a larger package. Also, the edge of the chip is prime real estate. External loop filters force the synthesizer to be in competition for edge space, subsequently making the layout more difficult.

Among the most challenging elements of synthesizer design is the loop filter. To alleviate loop-filter constraints, it is desirable to integrate the loop filter on the same chip as the synthesizer, and to make it programmable. An improved synthesizer architecture developed by Kaben Research (www.kabenresearch.com) called the "second-generation sigma-delta synthesizer" (Fig. 2) implements these two measures. It differs from precursors by integrating a sigma-delta phase detector and digital loop filter. A digital representation of the VCO phase and frequency is obtained using the sigma-delta phase detector and digital logic.

Since the phase- and frequency-measurement results are in the digital domain, it is possible to integrate a programmable digital loop filter and a digital frequency acquisition loop. This reduces the analog component of the loop filter to a single small-valued capacitor that can easily be integrated on chip. This capacitor is placed at the output of the current-mode DAC.

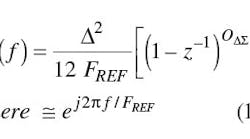

Apart from providing a digital representation of the VCO phase, the sigmadelta phase detector also features fractional phase resolution. This reduces the density of the phase quantization noise at the output of the synthesizer. In a sigma-delta fractional-N synthesizer, a sigma-delta modulator controls an integer-N divider in order to obtain fractional frequency resolution. The resulting quantization phase noise at the output of the synthesizer is given by:

where:

Δ = the quantization step size of the sigma-delta modulator,

OΔΣ= the order of the sigma-delta modulator, and

FREF = the reference frequency.

In this case, Δ has a step size of 1 VCO cycle, which is equal to 2 π radians. The sigma-delta phase detector introduces a phase quantization noise equal to:

Page Title

In this case, Δ is equal to 2∏/32, which results in a 30-dB reduction in total quantization noise power. In addition to the reduced quantization noise power, the second-generation synthesizer uses digital filtering to allow for more complex filtering to further attenuate the out-of-band quantization noise.

The synthesizer specifications from Table 2 were used to calculate phase noise plots for a traditional sigma-delta synthesizer (Fig. 3). The main requirement in this case was to have a phase noise of –140 dBc/Hz at a 3 MHz offset. The loop filter used in both cases is a standard integrator with phase lead correction and one additional pole to help filter quantization noise. In order to reduce the out-of-band phase quantization noise, the loop bandwidth of this conventional synthesizer was reduced to 7 kHz compared to the 35-kHz loop bandwidth used in the second-generation sigmadelta fractional-N synthesizer. This action significantly increases the inband phase noise of the traditional design compared to the second-generation approach for the same out-of-band phase noise (Fig. 4). While the conventional version could meet the same requirement with a loop bandwidth wider than 7 kHz and a more complicated loop filter, it would still be limited by the higher total phase quantization noise power.

The decreased out-of-band noise allows for much wider loop bandwidths. In cable modem applications, a higher loop bandwidth suppresses close-in VCO phase noise thereby permitting the use of low power VCOs. A wider loop bandwidth enables direct frequency modulation for wireless standards such as Bluetooth and GSM.

In a sigma-delta fractional-N synthesizer, direct modulation is only possible inside the loop bandwidth, beyond which any frequency components of the modulating data will be attenuated by the lowpass response of the loop. Pre-emphasis filtering can be used to compensate for the closed-loop bandwidth of the synthesizer (Fig. 5).

In direct modulation, it is possible to increase the modulation bandwidth and hence the data rate by using pre-emphasis. In order to effectively use pre-emphasis, it is necessary to know each of the loop transfer function parameters (for example, gain and time constants) with high accuracy in order to provide a filter that accurately compensates for the filtering of the phase-locked loop (PLL). This high accuracy is needed due to stringent modulation parameters in many standards. The analog loop filter component values can vary significantly over process and temperature causing all of the frequency transfer function parameters of the loop to vary. The VCO tuning gain also varies with process and temperature; however, it is a single gain parameter. This gain can be measured and compensated for using calibration. However, the variability in each of the other loop filter time constants is difficult to measure making highly accurate preemphasis filtering difficult if not possible to achieve. Therefore, if the variations in the loopfilter transfer function can be eliminated then we are left with the relatively simple task of measuring the VCO gain and compensating.

The loop filter in the new synthesizer, being mostly digital, has a predictable frequency response with process and temperature variations. Knowing the loop filtering characteristics with high accuracy allows the pre-emphasis filtering to push direct modulation to much higher data rates.

In the new synthesizer, the loop filter digital-to-analog converter (DAC) has a current-mode output (see Fig. 2). This combined with the capacitor forms an integrator with a gain determined by the capacitor value and DAC output current. The VCO tuning gain along with the gain of the DAC and the single capacitor value all lump into a single-gain parameter. By making the output current programmable over a wide range, the integrator gain can be changed to compensate for gain variations in the VCO tuning constant. By using a calibration algorithm and the VCO frequency measurement available in the second-generation sigma-delta fractional-N synthesizer, it is possible to perform this compensation automatically. This compensation allows the loop dynamics to be controlled with high accuracy allowing for stable loops over a wide range of frequencies, temperatures, and process variations.

Reference 6 shows that the limits to pre-emphasis are dynamic range limitations in the digital pre-emphasis filter and loop components. The reference frequency is also a limiting factor as it sets the maximum clock rate for the digital filter. As the modulation rate increases beyond the loop bandwidth, the loop filter attenuation of the data also increases. To compensate, higher amplification from the pre-emphasis filter is required until eventually the dynamic range limitations of the components are exceeded. The researchers in ref. 1 were able to achieve 2.85 Mb/s for a loop bandwidth of 84 kHz and a reference frequency of 20 MHz, a data rate to loop bandwidth ratio of ~ 29.

The second-generation sigma-delta fractional-N synthesizer with integrated loop filter is well suited to direct modulation. The reduced out-of-band quantization noise allows for increased loop bandwidth for a given phase-noise specification. This means that for a given modulation rate the dynamic range required in the digital filter is lower than would be required in a traditional fractional-N synthesizer. This in concert with the advantages of pre-emphasis and the VCO calibration enable high data-rate direct modulation architectures.

An example of a GSM modulator using second-generation sigma-delta fractional synthesis generation techniques is presented in refs. 7 and 8. Because the new synthesizer design can include the loop filter on chip, the synthesizer is no longer tied to the outer edge of the chip providing a great deal of layout flexibility and easy pin access.

A benefit for multi-mode systems is that the multiple VCOs can share the same DAC, capacitor, and sigma-delta phase detector. There is no need to have multiple loop-filter passive components for multiple standards or transmission bands. Loop filter design is limited only by the area allotted for digital circuitry, which will scale down as semiconductor processes evolve.

Page Title

A further benefit is that the second-generation sigma-delta fractional-N synthesizer has inherently faster acquisition for a given loop bandwidth than a traditional sigma-delta fractional-N synthesizer. This is because we measure both the frequency and phase of the VCO allowing us to incorporate a high gain frequency acquisition loop in the digital domain. Initial system level simulations for a 200-MHz frequency jump and a loop bandwidth of ~ 100 kHz indicate settling to 200 Hz in 30 µs.

The digital loop filter can also be implemented in VHDL and auto-placed and-routed with the rest of the synthesizer digital. An on-chip digital filter equivalent to a typical analog passive loop filter (see Fig. 1) would require less than one thousand gates. Given that digital filters are reconfigurable and relatively small in size, integrated multi-state filters required for multi-mode systems are now practical.

In summary, this next-generation synthesizer is a significant improvement over traditional sigma-delta fractional— synthesizers. The high accuracy of the fully integrated digitally programmable loop filter enables pre-emphasis, VCO calibration, and wider loop bandwidths A digital frequency-acquisition loop allows for much faster acquisition for a given loop bandwidth than a sigmadelta synthesizer. Systems architects are afforded increased flexibility as there are fewer trade-offs when designing multi-standard system-on-chip (SoC) devices.

REFERENCES

- W.T. Bax, T.A. Riley, C. Plett, and M.A. Copeland, "A Σ-Δ frequency discriminator based synthesizer," ISCAS ‘95: Proceedings of the 1995 IEEE International Symposium on Circuits and Systems, Vol. 1, pp. 1-4.

- Robert Bogdan Staszewski, Chih-Ming Hung, Ken Maggio, John Wallberg, Dirk Leipold, and Poras T. Balsara, "All-Digital Phase-Domain TX Frequency Synthesizer for Bluetooth Radios in 0.13-µm CMOS," 2004 IEEE International Solid-State Circuits Conference.

- Robert Bogdan Staszewski, John Wallberg, Sameh Rezeq, Chih-Ming Hung, Oren Eliezer, Sudheer Vemulapalli, Chan Fernando, Ken Maggio, Roman Staszewski, Nathen Barton, Meng-Chang Lee, Patrick Cruise, Mitch Entezari, Khurram Muhammad, and Dirk Leipold, "All-Digital PLL and GSM/EDGE Transmitter in 90nm CMOS," 2005 IEEE International Solid-State Circuits Conference.

- Robert Bogdan Staszewski, Dirk Leipold, and Poras T. Balsara, "Direct Frequency Modulation of an ADPLL for Bluetooth/GSM With Injection Pulling Elimination," IEEE Transactions on Circuits and Systems—II: Express Briefs, Vol. 52, No. 6, June 2005.

- Robert Bogdan Staszewski, Dirk Kipold, Chih-Ming Hung, and Poras T. Balsara, "TDC-Based Frequency Synthesizer for Wireless Applications," 2004 IEEE Radio Frequency Integrated Circuits Symposium, Phoenix, AZ.

- Perrott et al., "A 27-mW CMOS FractionalN Synthesizer Using Digital Compensation for 2.5-Mb/s GFSK Modulation," IEEE J. Solid-State Circuits, December 1997, Vol. 32, No. 12, pp. 2048-2060.

- W.T. Bax and M.A. Copeland, "A GMSK modulator using a ΔΣ frequency discriminator-based synthesizer," IEEE J. Solid-State Circuits, August 2001, Vol. 36, No. 8, pp. 1218–1227.

- W.T. Bax and M.A. Copeland, "A GSM modulator using a ΔΣ frequency discriminator based synthesizer," ISCAS ‘98: Proceedings of the 1998 IEEE International Symposium on Circuits and Systems, Vol. 4, pp. 498-501.