60-GHz IPIC-QVCO Reduces Phase Noise And Error

This file type includes high resolution graphics and schematics when applicable.

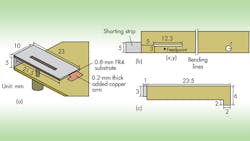

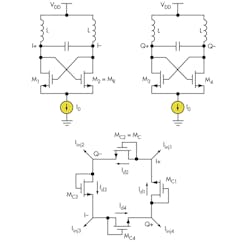

Designing a low-power CMOS phase-locked loop (PLL) operating at 60 GHz for a direct-conversion transceiver is quite tricky. For example, it is difficult to account for low phase noise/phase error and the wide-range operation necessary for high-data-rate wireless communications. To meet those design challenges, a research group from Singapore developed an integer-N, third-order, charge-pump PLL with a 135-MHz reference and an in-phase, injection-coupled (IPIC) quadrature voltage-controlled oscillator (QVCO). A paper describing the design of the IPIC-QVCO has been provided by Xiang Yi, Chirn Chye Boon, Hang Liu, Jia Fu Lin, and Wei Meng Lim.

A benefit of this design is that quadrature accuracy is not affected by the mismatches of the Q of the tank circuit and the current reference. But the mismatch of the coupling network does affect the quadrature accuracy as a function of phase error. Because the coupling network is composed of a symmetric design, the mismatches produced are minimal. In terms of phase error, this amounts to less than a 1 deg. error with a maximum 5% mismatch in the coupling network.

The circuit was simulated with 65-nm transistors, as they meet the frequency requirements of 60-GHz transmission. In a comparison with other simulated typologies of QVCOs, the IPIC-QVCO supposedly outperforms P-QVCOs, super-harmonic-coupled QVCOs, and magnetically coupled QVCOs when it comes to phase-noise and phase-error metrics. The experimental circuit in 65-nm CMOS covers 57.9 to 68.3 GHz while boasting phase noise from -89.8 to -91.0 dBc/Hz at 1-MHz offset from the carrier throughout the frequency of operation. See “A 57.9-to-68.3 GHz 24.6 mW Frequency Synthesizer With In-Phase Injection-Coupled QVCO in 65 nm CMOS Technology,” IEEE Journal Of Solid-State Circuits, Feb. 2014, p. 347.

This file type includes high resolution graphics and schematics when applicable.

About the Author

Jean-Jacques DeLisle

Jean-Jacques graduated from the Rochester Institute of Technology, where he completed his Master of Science in Electrical Engineering. In his studies, Jean-Jacques focused on Control Systems Design, Mixed-Signal IC Design, and RF Design. His research focus was in smart-sensor platform design for RF connector applications for the telecommunications industry. During his research, Jean-Jacques developed a passion for the field of RF/microwaves and expanded his knowledge by doing R&D for the telecommunications industry.

Leaders relevant to this article: