Fabricate a 2.4-GHz Fractional-N Synthesizer

This file type includes high resolution graphics and schematics.

Frequency synthesizers are used throughout communications systems for tuning the signal frequencies needed for receiving and transmitting. As silicon CMOS technology has been applied at higher frequencies, it has helped the expansion of wireless technology to a wide range of applications.1,2 In particular, these synthesizers have supported applications requiring tuning with fine resolution—from kHz steps to a few MHz—and low phase noise, on the order of -100 dBc/Hz offset 10 kHz from the carrier.

Related Articles • Synthesizer Consumes 400 μW To Support ISM • Small Synthesizer Spans 1.1 To 2.5 GHz • USB Synthesizer Extends To 9 GHzMany of these synthesizers have been developed as integrated-circuit (IC) solutions.3 In terms of circuit architectures, integer-N frequency synthesizers are often challenged in meeting performance requirements such as loop bandwidth, phase noise, and channel spacing due to the fundamental design of the integer-N divider modulus.

In contrast, a fractional-N frequency synthesizer can provide the loop bandwidths needed for many of these emerging wireless applications, with fine channel spacing. In addition, they can achieve low phase noise without excessive reference spurious levels. Since a fractional-N frequency synthesizer uses a higher phase/frequency-detector (PFD) comparison frequency and lower division ratio than an integer-N frequency synthesizer, low-frequency phase noise can be suppressed to a high degree in a fractional-N synthesizer.5

1. This simple block diagram shows the main components of a basic communications transceiver.

Figure 1 represents a typical RF wireless transceiver system, showing the role of the frequency synthesizer in both transmitter and receiver sections.6 Essentially, the frequency synthesizer must cover a required frequency range with adequate output power—as well as acceptable levels of signal integrity and signal purity—with the capability of tuning to meet channel spacing requirements.7 Locking or stabilizing the frequency synthesizer usually works around a specific frequency but, depending upon adjacent components, a synthesizer’s locking loop may favor other frequencies8 (Figs. 2-3).2. Locking at third harmonic.

3. Locking at adjacent frequency.

For example, harmonic locking can occur when harmonic frequencies have sufficient amplitude levels to engage the synthesizer’s locking loop. This type of locking usually occurs with square waveform modulation where multiples of the desired frequency have sufficient power to cause locking. Long runs of zeros in data bit causes phase detector favors fractional and non-fractional harmonics.9 Side-locking occurs when periodic modulation produces discrete spectral lines with enough energy to cause a synthesizer’s loop to lock to one of these spectral lines. This typically occurs in narrowband frequency synthesizers where the discrete spectral lines are very close, and have high enough amplitude to cause locking.

Spurious Products

The primary spurious frequencies generated in integer-N frequency synthesizers come from reference spurious signal products. The step size and loop bandwidth relationship dictate the spurious attenuation level that can be tolerated for a given synthesizer design. In contrast, spurious signal products in a fractional-N structure emanate from the fractional modulus. Fractional spurious signals appear around the voltage-controlled-oscillator (VCO) carrier frequency regardless of which frequency it is programmed to. The spacing between the first three spurious products is usually equal to the step size or one-half of the channel step size. In a fractional-N frequency synthesizer, the comparison frequency or step size is typically high, which leads to large loop-filter attenuation of the reference spur (even with a wide loop bandwidth implementation).

Boundary spurious products appear in an integer-N structure when the synthesizer’s VCO is programmed to frequencies near harmonic multiples of the comparison frequency. But all fractional-N synthesizers also exhibit these spurious products. These spurious signals are at lower amplitude levels than primary integer-N spurious products located at a harmonic of the comparison frequency. Whether or not these spurious products represent problems in a synthesizer design depends on the loop bandwidth, the comparison frequency, the system spurious specification, and the required frequency band plan (the actual LO channel frequency).

This file type includes high resolution graphics and schematics.

In a performance comparison, a fractional-N structure provides better step resolution and a faster locking process than an integer-N structure. With the latter, widening the loop bandwidth in order to increase the locking process and step size can cause reference spurious frequencies to emerge. In an integer-N synthesizer, the VCO divider (divider N modulus) integer is also large due to the low comparison frequency, resulting in poor phase-noise performance compared to a fractional-N synthesizer. Due to their fast switching times with fine resolution and acceptable phase noise, fractional-N synthesizers have been widely used in 2.5G and 3G wireless handsets.

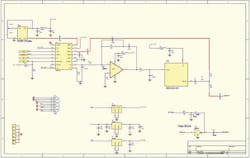

4. This pre-layout schematic diagram was created with the help of Protel design software.

Assembly

For assembling a fractional-N frequency synthesizer for use from 1.8 to 2.4 GHz, a model ROS-2432-119+ VCO IC from Mini-Circuits was one of the starting points for the design layout. It operates in the frequency band from 1.6 to 2.5 GHz with low phase noise of -100 dBc/Hz offset 10 kHz from the carrier. Also, a model ADF4118 integer-N frequency synthesizer IC from Analog Devices Co. capable of operating to 3 GHz was used in the synthesizer for division and phase-frequency detection (PFD). For the reference oscillator, a model TXO200U temperature-compensated crystal oscillator (TCXO) from Rakon Ltd. was used. It operates at 10 MHz with typical phase noise of -150 dBc/Hz offset 10 kHz from the carrier.

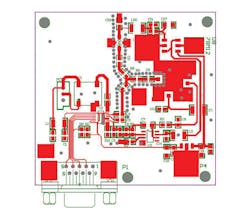

5. This layout represents the 1.8-to-2.4-GHz frequency synthesizer.

The primary spurious frequencies in this design are from reference spurious signals. The synthesizer step size and loop bandwidth relationship dictates the attenuation level of these spurious products. The spacing between the first three spurious products is usually equal to the step size or one-half the channel step size. For optimum reduction of spurious levels, a step size of 200 kHz and loop bandwidth of 100 Hz were established for the fractional-N frequency-synthesizer design. Widening the loop bandwidth would increase the locking speed and step size, but would also increase the number and levels of spurious products.

6. This photograph shows the fabricated 1.8-to-2.4-GHz frequency synthesizer.

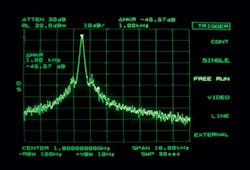

7. This screen shows a spectrum view of the synthesizer at 1.80 GHz.

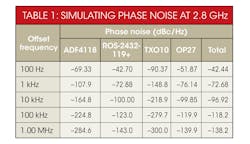

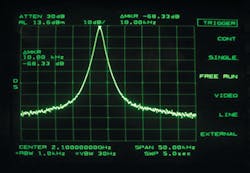

After validating the results from computer simulations (Fig. 4, Table 1), a printed-circuit-board (PCB) layout of the fractional-N frequency synthesizer was created with the help of Protel software (Fig. 5). This PCB design/layout software, which was originally developed by Altium (formerly Protel), is available for free download from a number of different websites. Altium also offers higher-level software tools, including Altium Design. The synthesizer was fabricated as a PCB (Fig. 6) and evaluated at center frequencies of 1.8 and 2.1 GHz (Figs. 7 and 8) with the help of a model HP8563A spectrum analyzer from Agilent Technologies.

8. This screen shows a spectrum view of the synthesizer at 2.10 GHz.

Related Articles • Synthesizer Consumes 400 μW To Support ISM • Small Synthesizer Spans 1.1 To 2.5 GHz • USB Synthesizer Extends To 9 GHzSpurious performance is less impressive at 2.1 GHz than at 1.8 GHz. The bandwidth for the 1.8-GHz measurements was narrower, meaning that the phase-noise performance will be superior at the lower band frequencies. The spectrum analyzer’s span was set to 50 kHz, with a resolution-bandwidth (RBW) filter at 1 kHz and a video-bandwidth (VBW) filter set at 10 Hz. The 55.67-dB power difference between the carrier and the phase noise, offset 10 kHz from the carrier, indicates that the phase noise level will be:

Phase noise (at 2.1 GHz) = -68.33 – 10log(RBW) = -98.33 dBc/Hz.

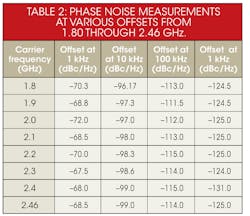

The fractional-N frequency synthesizer was evaluated for phase noise at carrier frequencies from 1.8 to 2.4 GHz at 100-MHz intervals and for offset frequencies of 1 kHz, 10 kHz, 100 kHz, and 1 MHz. The results are compiled in Table 2. The synthesizer achieved respectable phase-noise performance, with a level of -98 dBc/Hz offset 10 kHz from the carrier. The design is applicable to a number of wireless systems, including for Bluetooth, DCS, GSM, and wireless-local-area-network (WLAN) systems.

References

1. H. Ameri, A. Attaran, and M. Moghavvemi, “Planning of low-cost 77-GHz radar transceivers for automotive applications,”IEEE Aerospace and Electronic Systems Magazine, Vol. 27, 2012, pp. 25-31.

2. M. Moghavvemi, A. Attaran, and H. Ameri, “Design an X-band frequency synthesizer,”Microwaves and RF, Vol. 49, 2010, pp. 98-103.

3. M. Moghavvemi, H. Ameri, and A. Attaran, “Design a stable 14-to-20-GHz source,”Microwaves and RF, Vol. 49, No. 12, December 2010, pp. 62-66.

4. M. Moghavvemi and A. Attaran, “Performance Review of High-Quality-Factor, Low-Noise, and Wideband Radio-Frequency LC-VCO for Wireless Communication,”IEEE Microwave Magazine, Vol. 12, 2011, pp. 130-146.

5. M. Moghavvemi and A. Attaran, “Recent Advances in Delay Cell VCOs,”IEEE Microwave Magazine, Vol. 12, 2011, pp. 110-118.

6. H. Ameri and M. Moghavvemi, “Assemble a ku-band frequency synthesizer,”Microwaves and RF, Vol. 48, 2009.

7. M. Moghavvemi, H. Ameri, and A. Attaran, “Fabricate an 8.35-GHz frequency synthesizer,”Microwaves and RF, Vol. 50, 2011.

8. M. Moghavvemi, H. Ameri, and A. Attaran, “A Compact Analytical Design of Dual-Loop 18-GHz Frequency Synthesizer to Enhance signal reliability in Digital Millimeter Radio Link System,”Frequenz, Vol. 65, 2011, pp. 29-35.

9. M. Moghavvemi, H. Ameri, and A. Attaran, “Assembly of Low Phase noise Sub-Millimeter Wave Local Oscillator in Ku Band Frequency,”presented at the UMIES2011, Kuala Lumpur, 2011.

This file type includes high resolution graphics and schematics.